服務熱線

0755-83044319

發布時間:2023-04-11作者來源:印寧華瀏覽:4514

SerDes簡介

首先我們要了解什么是SerDes,SerDes的應用場景又是什么呢?SerDes又有哪些常見的種類?做過FPGA的小伙伴想必都知道串口,與并行傳輸技術相比,串行傳輸技術的引腳數量少、擴展能力強、采 用點對點的連接方式,而且能提供比并行傳輸更高帶寬,而SerDes的主要作用就是把并行數據轉化成為串行數據,或者將串行數據轉化為并行數據的“器件。

SerDes的全稱是SERializer(串行 器)/DESerializer(解串器),這種主流的高速的時分多路復用(TDM),點對點的串行通信技術可以充分利用通信的信道容量,提升通信速度,進而大量的降低通信成本。目前,商用基于SerDes架構的通信協議[敏感詞]可實現單通道56Gbps(好像已經可達112Gbps)的速率,在未來高帶寬、低成本的應用領域會 越來越廣泛。

實際上PCIE,JESD204B等復雜協議都是基于SerDes協議,常見的電SerDes就PCIE等協議來說,更接近物理層,所以SerDes通常又被稱之為物理層(PHY)器件。正是因為SerDes的強電氣屬性,使得 Serdes具有以下優點:

1.減少布線沖突(非獨立時鐘嵌入在數據流中,解決了限制數據傳輸速率的Signal時鐘的Jilter問 題);帶寬高 ;2.引腳數目少 ;3.抗噪聲、抗干擾能力強(差分傳輸);4.降低開關噪聲;5.擴展能力強;6.更低的功耗和封裝成本;

根據SerDes的結構的不同可以將其分為四類:

并行時鐘SerDes:將并行寬總線串行化為多個差分信號對,傳送與數據并聯的時鐘。這些SerDes 比較便宜,在需要同時使用多個SerDes 的應用中,可以通過電纜或背板有效地擴展寬總線;

8B/10B編碼SerDes(最常見的結構):將每個數據字節映射到10bit代碼,然后將其串行化為單一 信號對。10位代碼是這樣定義的:為接收器鐘恢復提供足夠的轉換,并且保證直流平衡(即發送相 等數量的‘1’和‘0’)。這些屬性使8B/10B編碼SerDes 能夠在有損耗的互連和光纖傳輸中以較少的信 號失真高速運行;

嵌入式時鐘SerDes:將數據總線和時鐘串化為一個串行信號對。兩個時鐘位,一高一低,在每個 時鐘循環中內嵌串行數據流,對每個串行化字的開始和結束成幀,并且在串行流中建立定期的上升 邊沿。由于有效負載夾在嵌入式時鐘位之間,因此數據有效負載字寬度并不限定于字節的倍數;位交錯SerDes:將多個輸入串行流中的位匯聚為更快的串行信號對。

SerDes支持非常多的的主流工業標準,比如Serial RapidIO ,FiberChannel(FC),PCI-Express (PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。

SerDes結構

實上在SerDes收發器內部包括高速串并轉換電路、時鐘數據恢復電路、數據編解碼電路、時鐘糾 正和通道綁定電路,為各種高速串行數據傳輸協議提供了物理層(PHY)基礎。而主流的8B/10B編 碼SerDes則主要由物理介質相關子層( PMD)、物理媒介適配層(Physical Media Attachment,PMA)和物理編碼子層( Physical Coding Sublayer,PCS )所組成,且收發器的 TX發送端和RX接收端功能獨立。

SerDes收發器內部的電路物理層結構圖

各物理層的作用:

1.PCS層,負責數據流的編碼/解碼,是標準的可綜合CMOS數字邏輯,可以通過邏輯綜合實現 軟硬綜合實現。2.PMA層,是數模混合CML/CMOS電路,負責負責串化/解串化,是理解SerDes區別于并行接 口的關鍵。3.PMD層,負責串行信號通信。

涉及模塊:

1.TXPLL:這個模塊主要使用具有1ps以下的抖動的時鐘為參考,輸出數GHZ級的時鐘。2.RXCDR(時鐘恢復):這個模塊是一個復雜的控制回路,作用是來追蹤傳入數據的平均相位, 并不管Path上的任何SI或失真,通常是通過復雜的相位旋轉器或CDR驅動的鎖相環來完成的。3.TXdriver:這個模塊把序列化模塊轉化為差分信號。4.RX均衡器:此模塊用連續的時間均衡器以及DFE(裁決反饋均衡器)來均衡高速效應,通常 需要一個自動增益的電路來促進均衡效果,RX均衡器通常以狀態機邏輯和軟件的形式來實現 自動校準。

轉化過程:

1.發送(TX)即并轉串 簡單的來說就是并行信號通過FiFO,傳遞給內部的8b/10b編碼器、擾碼器,防止數據連0/1, 之后傳遞給串行器進行轉化,經過均衡器均衡后,由驅動發出。

2.接收(RX)即串轉并 簡單的來說就是輸入的串行信號經過線性均衡器均衡后,去除了高速時鐘的jilter后,CDR從數 據中恢復Caputure時鐘,并通過解串器轉為對齊的并行信號,由驅動發出。

光SerDes解串器

目前光互連中電串行/反串行器(SerDes)的高功耗和速度提升障礙是光互連發展的阻礙,人們逐 漸把目光投向光SerDes的高速收發器。光SerDes解串器采用時間交錯的多路復用技術來進行并行 串行光信號的直接轉換,同時電SerDes的缺失極大地降低了數據傳輸通道中的功耗,以一個工作在 20個數據速率為2GHz的并行數字路徑和1個40GHz串行光通道之間的光SerDes收發器為例,其功 耗僅為13.5pJ/b左右,要遠遠低于同類型電SerDes的靜態功耗。同時結合波分復用(WDM)、脈沖幅 度調制(PAM)、正交相移鍵控(QPSM)等多種光復用技術,可進一步提高帶寬。

在數據中心、超級計算機和光纖接入網的數據通信中,對未來帶寬的需求不斷增長,這促使傳 統的電子鏈路被光鏈路取代,用于片內和片外通信。雖然光學技術在帶寬、損耗、串擾、電磁兼容 等方面具有優勢,但由于光信號不能直接由處理器處理,需要將光信號轉換為電信號。傳統的光互 連通信解決方案是將并行電信號通過芯片內部的串行器/反串行器(SerDes)轉換為高速串行電信號, 再通過芯片外部的光收發器轉換為光信號。由于SerDes電路的高功耗和鏈路比特率,光互連的發展 逐漸面臨瓶頸。收發器的大部分功率消耗在模擬電路,特別是SerDes上,而不是光學器件上。

以當前28Gb/s系統為例,收發器的光電轉換(EO)和光電轉換(OE)功耗僅為7.2pJ/b。但是整個 鏈路的功率預算增長到29.5pJ/b,其中22.3pJ/b(75.6%)是由SerDes電路貢獻的,這與OE-EO轉換 沒有直接關系。進一步的帶寬擴展受到嚴重限制,因為需要均衡來恢復信號完整性,并在高速串行 鏈路的末端重新計時,即使是非常短的幾英寸距離。同時提高比特率和保持低功耗是不可持續的。因此,[敏感詞]是提高并行度來提高鏈路比特率。但是并行化程度的提高是由芯片的引腳數決定的,而 引腳數是由制造工藝、芯片尺寸、芯片頂層設計等決定的。

簡單地說,光SerDes就是利用時分復用技術將并行電信號加載到光載波上,獲得單波長單通道 電平可能高于40Gb/s的串行光傳輸,同時完成光電和串并聯轉換。如圖3所示,傳統的電子SerDes 收發器需要兩級轉換,以高速串行電信號為介質,將低速并行電信號轉換為高速串行光信號,而光 SerDes收發器實現了低速并行電信號與高速串行光信號的直接轉換,即比傳統的電SerDes多了一 級光電信號轉化。

兩種收發器的比較。(a)在傳統收發器中,以高速串行電信號為介質,利用電子SerDes將并行 電信號轉換為高速串行光信號。(b)在所提出的收發器中,利用光SerDes將并行電信號直接轉換為 高速串行光信號。

SerDes主要包括以下幾個部分:

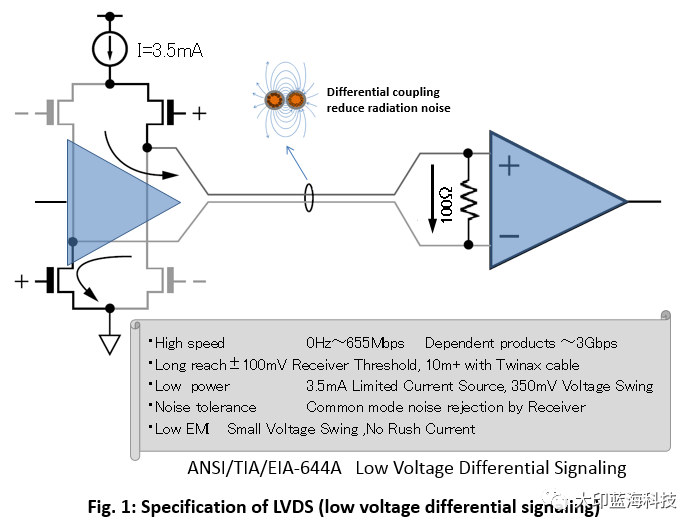

1、SerDes的前輩:LVDS SerDes,其中LVDS應該是大家比較熟悉的,這里不會展開,主要就是LVDS是1995年作為「ANSI/TIA/EIA-644」制定了標準規格的串行接口用物理層規格,為很多串行差分總線的發展奠定了基礎。

2、SerDes底層硬件包括早期的LVDS和現在CML:SerDes信號層采用的LVDS工作在155Mbps~1.25Gbps之間,而CML(電流模式信號)在600Mbps和10+ Gbps。因此現在SerDes一般使用CML。但是LVDS和CML信號可以互通,但要有外接電阻做電平轉換。LVDS SerDes的基本原理理解串行總線高速、遠距離、低雜音的特征.

針對LVDS、CML等差分技術會詳細的介紹;上面已經詳細介紹了LVDS,在閱讀文檔時,還時常看到CML、LVPECL,那么這些差分信號之間的差別是什么?

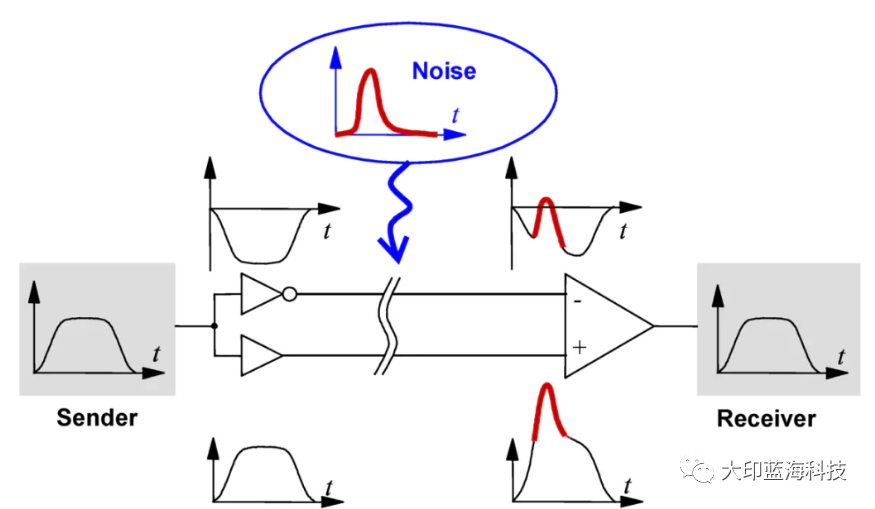

差分技術:LVDS、MLVDS、CML、LVPECL的區別與應用場景平衡型差分傳輸Differential Transmission 是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的非平衡型單端Single End Transmission 做法,差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相同,相位相反。在這兩根線上的傳輸的信號就是差分信號。信號接收端比較這兩個電壓的差值來判斷發送端發送的邏輯狀態。在電路板上,差分走線必須是等長、等寬、緊密靠近、且在同一層面的兩根線。

差分信號示意圖

差分信號與傳統的一根信號線一根地線(即單端信號)走線的做法相比,其優缺點分別是。

優點:

1.抗干擾能力強。干擾噪聲一般會等值、同時的被加載到兩根信號線上,而接收端關心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

2.能有效抑制電磁干擾(EMI)。由于兩根線靠得很近且信號幅值相等,這兩根線與地線之間的耦合電磁場的幅值也相等,同時他們的信號極性相反,按右手螺旋定則,那他們的磁力線是互相抵消的。兩根線耦合的越緊密,互相抵消的磁力線就越多。泄放到外界的電磁能量越少。

3.時序定位準確。差分信號的接收端是兩根線上的信號幅值之差發生正負跳變的點,作為判斷邏輯0/1跳變的點的。而普通單端信號以閾值電壓作為信號邏輯0/1的跳變點,受閾值電壓與信號幅值電壓之比的影響較大,不適合低幅度的信號。

4.發送端電流源始終導通,消除開關噪聲帶來的尖峰(單端技術中所需要)和大電流晶體管不斷導通-關斷造成的電磁干擾EMI。

缺點:

若電路板的面積非常吃緊,單端信號可以只有一根信號線,地線走地平面,而差分信號一定要走兩根等長、等寬、緊密靠近、且在同一層面的線。這樣的情況常常發生在芯片的管腳間距很小,以至于只能穿過一根走線的情況下。

幾種典型差分信號

為了實現高速數據傳輸,有多種差分技術可供選擇。這些差分技術都有差分信號幾個共同的優點,但是在性能、功耗和應用場景上有很大的區別。下圖列舉了最常用的幾種差分信號技術和它們的主要參數。

各種差分技術的工業標準

LVDS信號擺幅低,為350mv,對應功耗很低,速率達到3.125Gbps。總的來說,終接方法簡單、功耗和噪聲低等優點,使得LVDS成為幾十Mbps至3Gbps、甚至更高的應用之[敏感詞]。

我們可以毫不夸張地說--LVDS(Low voltage differential signaling)技術開拓了串行接口的歷史。在1990年代中期,LVDS SerDes(串行轉換器/串行解串器)被使用于市場需求急速擴大的筆記本電腦上,銷售數量急劇猛增。LVDS為筆記本電腦在世界上的普及起到了一定的作用,為液晶顯示器在市場上站穩腳跟做出了很大的貢獻。

使用于筆記本電腦的LVDS SerDes在那之后,被集中用于電腦用芯片組和液晶時間控制器IC(TCON),以應對UXGA和WUXGA之類高分辨率液晶屏所需,被持續使用了15年以上。筆記本應用上從2012年左右開始慢慢被eDP(embedded DisplayPort)替換。但可以說LVDS SerDes直到近期仍是支撐著筆記本電腦市場的存在。

但LVDS SerDes并不是連接液晶顯示屏和邏輯板的“專用”接口技術。分析一下這一技術的內容就會一目了然--它是一種連接A點與B點的普通的串行接口技術。因此,他可以在各種不同的接口用途上適用。那么在哪些用途上如何使用才能更好地發揮出LVDS SerDes的性能呢?下面我們就來詳細說明。

發揮高速的數據傳輸的作用

要靈活使用LVDS SerDes,首先需要理解物理層面的LVDS技術。

LVDS是1995年作為「ANSI/TIA/EIA-644」制定了標準規格的串行接口用物理層規格(圖1)。通過驅動3.5mA的穩定電流電源,可在100Ω終端時,以350mV這樣非常低振幅的差動信號來高速傳送數據。其數據傳輸速度在規格內限定[敏感詞]為655Mbit/秒。但這并不是極限值。通過各半導體廠商獨有的加工,可以完成3Gbit/秒左右的高速傳輸速度。

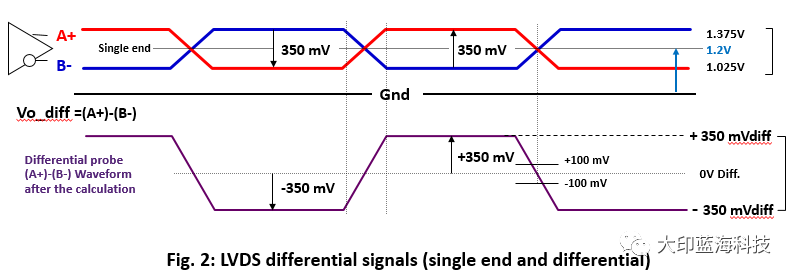

LVDS的差動信號波形的具體示例請見圖2。

將2根差動信號--正電極信號(A+)和負電極信號(B?),以1.2V的共同電壓(Voc)為中心,使2個信號間以350mV的電位差擺動。然后,用探針測定示波器的差動,會得到圖2這樣的信號波形。這就是兩個信號的振幅差((A+)?(B?))。以差動探針測定,就能得到振幅差的計算結果。但是這樣的信號波形并不是物理存在的。

圖3是LVDS接收器的共通電壓范圍。

如圖所示:LVDS接收器其可收信的共通電壓范圍很廣。送信(發送機)方以1.2V的共通電壓輸出后,收信(接收器)方的共通電壓只要在0.2~2.2V的范圍內就能接收信號。

此外,LVDS SerDes是以低振幅的差動信號來傳送數據,因此可以抑制多余的輻射雜音(EMI:Electro-Magnetic Interference);防止EMI混入其他的回路中造成不良影響之類的事態發生。這也是它多被使用在對雜音較敏感的電子設備上的理由之一。

也就是說LVDS SerDes具備能高速和遠距離地傳輸數據、對共通電壓耐性高,且多余輻射少等優點。它最合適的用途就是用于需要這些優點的電子設備上。比如復合機(MFP)。

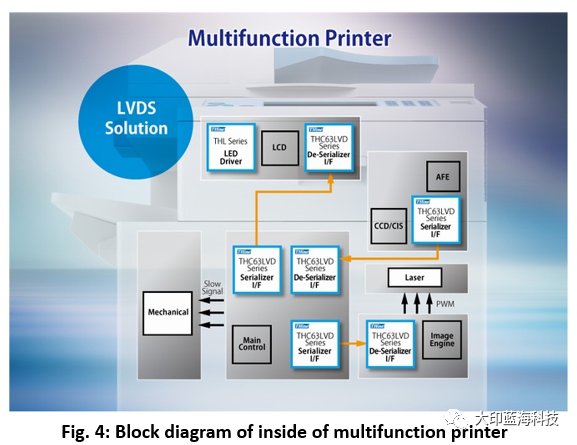

LVDS SerDes在MFP中除了可以用于液晶顯示用接口以外;將掃描儀(圖像傳感器)取得的圖像數據傳送到實行圖像處理的主板上時也可使用。裝置內其實有一定的距離(圖4)。使用LVDS SerDes的話,掃描儀與主板相距較遠也沒問題。雖然與所使用的配線的扭曲度和電力損失程度有一點關系,但僅用細小的配線傳輸數米之類的完全不會成問題。對于這類需要機箱內高速數據傳輸的電子設備,LVDS SerDes可以被很好地應用。

對配線扭曲和共通電壓耐性強

現在,LVDS SerDes有多種產品在銷售中。接下來將以THine Electronics的產品系列為例進行詳細介紹。

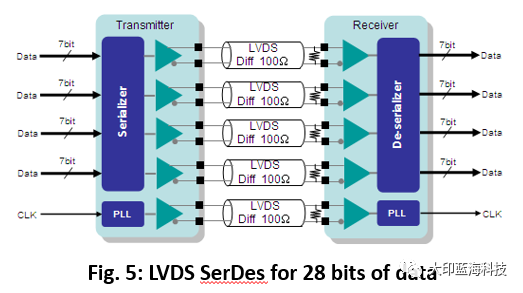

圖5是LVDS SerDes的基本構成。

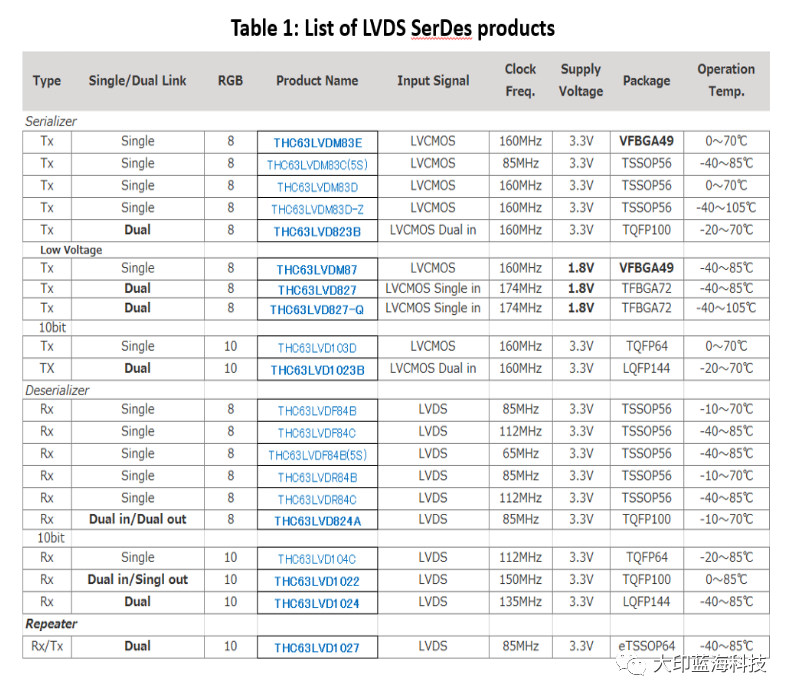

輸入串行轉換器的信號數據為7bit×4根=28bit。將這些數據轉換成串行的LVDS信號,傳輸到串行解串器上。同時另行傳送時鐘信號。串行解串器會通過傳送到的時鐘信號調整時間來接收信號,將7bit×4根的LVDS信號轉換成TTL/CMOS數據并輸出。THine Electronics提供的LVDS SerDes的特征可列舉為以下6點(表1)。

1、在工作電壓為3.3V的普通產品以外,可在串行轉換器上按照LVDS規格的同時提供1.8V的低工作電壓的產品。一般情況下電源電壓降低,LVDS規格中限定的1.2V的輸出共通電壓(Voc)就很難保持。在一些同行業的競爭對手生產的低電壓產品中,Voc就常常會低于1.2V。但THine Electronics的「THC63LVDM87」和「THC63LVD827」可在達到1.8V的低工作電壓環境時,輸出共通電壓(Voc)在到達收信側的串行解串器時仍能維持最合適的1.2V。

2、產品涵蓋可應對單連接和雙連接的各個系列。比如RGB各10bit的圖像信號傳送用單連接的串行轉換器「THC63LVD103D」和串行解串器「THC63LVD104C」,其雙連接版則為串行轉換器「THC63LVD1023B」和串行解串器「THC63LVD1024」。使用雙連接產品可以簡單地使數據傳送帶寬放大。比如單連接產品最多只能對應1080I;但使用雙連接產品可以對應1080P。此外,我們還有RGB各8bit的雙連接產品,具體產品有串行轉換器「THC63LVD823B」和串行解串器「THC63LVD824A」等。這些產品可以應用于基板間及機箱內通路寬度較寬的數據通信用途上。

3、我們還有可以選擇使用脈沖上升沿或脈沖下降沿來控制取得數據的時間的產品。在液晶屏等用途上會用脈沖下降沿;但一般的數據傳輸時所使用的串行接口則會使用脈沖上升沿。我們的產品中產品型號上如LVDR這樣帶「R」的產品是對應使用脈沖上升沿的;LVDF這樣帶「F」的產品則是對應使用脈沖下降沿。「LVDM」和「LVD」的產品則可以同時對應兩種方式;可以通過pin設定來決定使用哪一種。

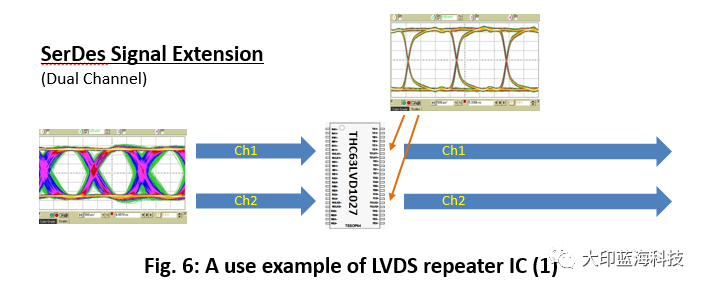

4、我們還有RepeaterIC產品。型號是「THC63LVD1027」。使用RepeaterIC,可以在接收LVDS SerDes輸出的信號后,吸收通過配線時產生的扭曲及波動,調整成電壓軸和時間軸都在理想狀態下的LVDS信號后再一次傳輸(圖6)。

這樣就可以使數據的傳輸距離(配線長度)大幅度加長。將其設置在傳送路徑的中部可使傳送距離(配線長度)延伸2倍。此外,還能使至今仍很困難的1個頻的圖像信號輸入分配到2頻這樣一種LVDS SerDes的信號分配成為可能(圖7)。

5、可對應的時鐘頻率范圍在8M~160MHz這一較大范圍。比如「THC63LVD103D」等產品就能對應較大的時鐘頻率范圍。頻率范圍大就能適用于各種并串通路;也能提高設計的靈活性。

6、我們還有將LVDS的輸出控制在更低振幅的產品。如前所述:LVDS SerDes一般在3.5mA的電流電源與100Ω的終端阻力下使用。因此振幅也在350mV。使用LVDS低振幅型的RS(Reduce Swing),可使振幅降低到200mV。因此可以抑制EMI達到低耗電。

此外,我們還有適合搭載在攝像機模組等小型電子設備上的、實際面積為5mm×5mm及超小的49pin VFBGA封印產品;適用車載設備的則有工作溫度范圍在?40~+105℃這樣廣的范圍下的產品;這些都是我們的特點。

綜上所述,THine Electronics有著眾多LVDS SerDes產品,可以對應各種不同用途。但是,僅靠LVDS SerDes還不能滿足所有的串行接口需求。要對應要求有4K的倍速和鮮艷的色彩、8K這樣的高分辨率信號以及高速的遠距離傳輸的用途就比較困難。因此THine Electronics開發出了更高速的串行接口技術。

關于HDMI 采用的TMDS過渡調制差分信號

過渡調制差分信號,也被稱為最小化傳輸差分信號(TMDS:Transition Minimized Differential signal),是指通過異或及異或非等邏輯算法將原始信號數據轉換成10位,前8位數據由原始信號經運算后獲得,第9位指示運算的方式,第10位用來對應直流平衡(DC-balanced,就是指在編碼過程中保證信道中直流偏移為零,電平轉化實現不同邏輯接口間的匹配),轉換后的數據以差分傳動方式傳送。

過渡調制差分信號,也被稱為最小化傳輸差分信號,是指通過異或及異或非等邏輯算法將原始信號數據轉換成10位,前8位數據由原始信號經運算后獲得,第9位指示運算的方式,第10位用來對應直流平衡(DC-balanced,就是指在編碼過程中保證信道中直流偏移為零,電平轉化實現不同邏輯接口間的匹配),轉換后的數據以差分傳動方式傳送。這種算法使得被傳輸信號過渡過程的上沖和下沖減小,傳輸的數據趨于直流平衡,使信號對傳輸線的電磁干擾減少,提高信號傳輸的速度和可靠性

在上世紀九十年代晚期,Silicon Image公司開始采用面板連接、數字可視接口(DVI)和高清多媒體接口(HDMI)的形式向顯示行業推廣其所有權標準——最小化傳輸差分信號(TMDS:Transition Minimized Differential signal)。在該情況下,發射端混合了具有在銅導線上降低EMI特性的更高級編碼算法,從而使得接收端具有健壯的時鐘恢復性能。

8位/10位編碼是一個二階處理,它是將一個8位的輸入信號轉換成10位的編碼。和LVDS相似的是,它采用了差分信號來降低EMI及提高精確的信號傳輸速率。還和LVDS相似的是,它是一個串行的傳輸設計。

應用: DVI技術已成功的應用于PC領域,HDMI技術也成功的推向了消費電子市場。但是,TMDS并沒有因此成為廣泛使用的面板接口標準。相反,沒有專利費的LVDS已被普遍使用。此外,當前的DVI版本并不能更新,而且具有物理上、功能上及成本上的局限。

目前HDMI高清線普遍采用的就是TMDS算法,HDMI把視頻信號分為R、G、B、H、V五種信號用TMDS技術編碼。TMDS把這三個通道傳輸R、G、B三原色,HV編碼在B信號通道里面傳輸,R、G的多余位置用來傳輸音頻信號。

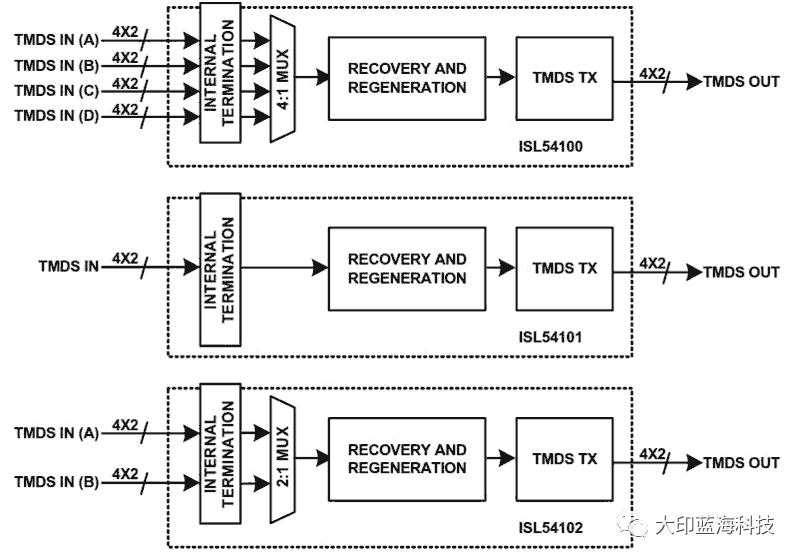

HDMI 4:1 Mux & Repeater - ISL54100 (with CDR Regeneration)

免責聲明:本文采摘自“大印藍海科技”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號