服務熱線

0755-83044319

發布時間:2022-03-18作者來源:薩科微瀏覽:5108

射頻器件的挑戰與創新

在從4G到5G的演進過程中,射頻器件的復雜性逐漸增加,產品在設計、工藝、材料等方面也發生了逐步的變化。 同時,射頻前端面臨功耗、尺寸、天線數量、芯片設計、溫度漂移、信號干擾、不同類型信號和諧共存等諸多技術挑戰。 如何解決這些問題是當今工業和射頻器件創新的重點。 隨著半導體材料的發展,通過替代Si、GaAs、GaN等RF材料以及陶瓷、玻璃等封裝基板材料,提高功耗、效率、發熱、尺寸等當然很重要。 用于開發射頻設備。 革新。 但除了材料創新,射頻器件還有哪些創新方式?

制造工藝

目前,射頻器件涉及的主要工藝為GaAs、SOI、CMOS、SiGe等。

GaAs:GaAs的電子遷移速率較好,適合用于長距離、長通信時間的高頻電路。GaAs元件因電子遷移速率比Si高很多,因此采用特殊的工藝,早期為MESFET金屬半導體場效應晶體管,后面演變為HEMT(高速電子遷移率晶體管),pHEMT(介面應變式高電子遷移電晶體),目前為HBT(異質接面雙載子晶體管)。

GaAs生產方式和傳統的硅晶圓生產方式大不相同,GaAs需要采用磊晶技術制造,這種磊晶圓的直徑通常為4-6英寸,比硅晶圓的12英寸要小得多。磊晶圓需要特殊的機臺,同時砷化鎵原材料成本高出硅很多,最終導致GaAs成品IC成本比較高;

SOI:SOI工藝的優勢在于可集成邏輯與控制功能,不需要額外的控制芯片;

CMOS:CMOS工藝的優勢在于可以將射頻、基頻與存儲器等組件合而為一的高整合度,并同時降低組件成本;

SiGe:近年來,SiGe已成了最被重視的無線通信IC制程技術之一。依材料特性來看,SiGe高頻特性良好,材料安全性佳,導熱性好,而且制程成熟、整合度高,具成本較低的優勢。SiGe既擁有硅工藝的集成度、良率和成本優勢,又具備第3到第5類半導體(如砷化鎵(GaAs)和磷化銦(InP)在速度方面的優點。只要增加金屬和介質疊層來降低寄生電容和電感,就可以采用SiGe半導體技術集成高質量無源部件。

SiGe工藝幾乎能夠與硅半導體超大規模集成電路中的所有新工藝技術兼容,是未來的趨勢。不過SiGe要想取代砷化鎵的地位還需要繼續在擊穿電壓、截止頻率、功率等方面繼續努力。

射頻PA采用的工藝分別是GaAs、SOI、CMOS和SiGe;射頻開關采用SOI、GaAs工藝;LTE LNA采用的工藝多為SOI、CMOS。

進入5G時代,Sub-6GHz和毫米波階段各射頻元器件的材料和技術可能會有所變化。SOI有可能成為重要技術,具有制作多種元器件的潛力,同時后續有利于集成。

格芯Chaojing Li和Randy Wolf討論了低噪音放大器(LNA)理論以及在6 GHz以下的應用(GPS,蜂窩網絡,Wi-Fi)使用RF-SOI和SiGe技術規格的設計考慮。兩位演講專家來自于較早前被收購的IBM Microelectronics,Randy擅長于高速加重器、數字功率檢測、PA及Data Converter, 還包括各類無線應用上的開關,LNA, PA, 負壓電苛泵及邏輯控制. 擁有22項專利和布魯塞爾大學本科及MIT碩士學歷; Chaojing有設計LNA, PA, Switchers, VCO, Power Dividers, Couplers, Power Detectors, Phase Shifters, Mixers, Sub-G for WLAN and Satlite application, 發表學術論文20篇并擁有四川大學本科和克雷頓大學博士學歷。

本次網絡研討會涵蓋的主題將包括:

+ 典型的6 GHz以下應用(GPS,蜂窩網絡,Wi-Fi)和規格

+ 基本的LNA理論

+ LNA的設計注意事項:

- 將LNA移動到前端模塊的優點

- GPS,蜂窩網絡和Wi-Fi應用的設計權衡和技術考慮

- RF-SOI和SiGe在LNA中的性能

擴展閱讀

如何理解/偏置cascode

電流鏡作用:復制電流、有源負載...

電流鏡參數:電流匹配、輸出阻抗、輸出電壓范圍、電源抑制比。

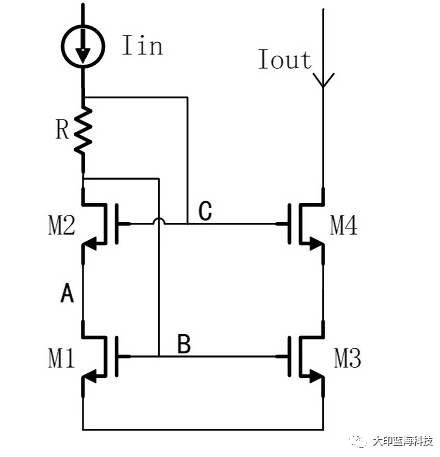

比較常用的是cascode

cascode電流鏡的電流源精度主要由M1和M3的匹配程度決定,而與M2和M4的匹配程度關系不大,所以:

在版圖上需要好好匹配的是M1和M3,而不是M2與M4。

同樣的在根據PDK中的“mismatch report”中提供的sigma計算W/L的時候,也是計算M1和M3的面積。

現在解釋一下為什么cascode的反饋結構近似是"電流—電壓負反饋"

↘Vt增大,輸入電流增大

↘Vb1電壓固定,所以增大的是VA

↘VA=Iout*ro1(采樣輸出電流Iout,轉換成電壓VA)

↘而A點又是跨導放大器M2的反向輸入端

↘VA增大,Vb2不變,VGS2減小

↘VGS2減小,Iout減小

以上過程采樣輸出電流,反饋到跨導放大器反向輸入端,與Vb2相減(做電壓相加減),減小電流。所以勉強可以認為cascode是一個“電流-電壓負反饋”結構。那么根據電流電壓反饋對輸出阻抗的影響,最初阻抗是ro1被放大了(1+gm2ro2)倍:

Rout=ro1*(1+gm2ro2)

≈gm2*ro2*ro1

與通過小信號電路"嚴密"計算的結果對比:

Rout=(1 + gm2·ro2)ro1 + ro2

≈gm2*ro2*ro1

可以看兩個結果基本一致.

下圖是我以前看Razavi的時候整理的反饋類型對阻抗影響的結論,可供參考。顯然M2和M4在環路中提供了主要增益,所以M2和M4在這里提供的是增益。

也就是說:如果非得說M2和M4的也影響電流鏡精度,那影響點就在他們的本征增益(gm·ro),M2和M4在這種結構中體現的是運放的角色,他們的W/L越大,電流鏡越“硬”,也就是輸出阻抗越大。

用電阻偏置

為了M2和M4飽和:

VB-VC≥Vt2

也就是:

IR≤Vt2

為了M1和M3在飽和區:

VC≥VB-Vt1+Vov2+Vt2

VC≥Vov2+(Vt2-Vt1)

結論:

Vov2+(Vt2-Vt1)≤IR≤Vt2

以上利用電阻的偏置方法中,電阻的阻值受工藝的影響較大,還有就是消耗電壓

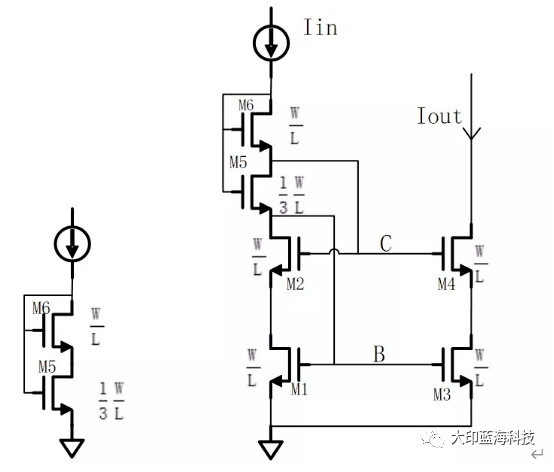

用MOS代替電阻

類比使用電阻偏置的情況可以得知:

Vov2<VDS5<Vt2

如果M5在飽和區,且尺寸又小,所以一定可以實現 Vov2<VDS5,但是很明顯M5在線性電阻區,所以我們計算VDS5=Vov2的情況:(讓M5的尺寸小于計算結果即可)

類比電阻偏置還有一個條件是,VDS5<Vth,在這里就不計算了可通過仿真得到,不能太小這樣不僅消耗了電壓裕度,而且可能讓M2和M4飽和,用這種方法的優點是,沒有電阻,減輕了工藝的影響。但是也消耗了電壓裕度。

用第三路偏置

類比方法2 的計算過程,同樣適用于方法3,所以將M5和M6合并成一個管子,所以M7的尺寸應該比M1小4倍,但是方法三的缺點是多了一路電流,優點是不消耗電壓空間。

本文主要寫了cascode的提高阻抗的原因,以及三種偏置辦法。

免責聲明:本文轉載自“大印藍海科技”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號