服務熱線

0755-83044319

發布時間:2022-04-11作者來源:印寧華瀏覽:5738

在傳統以及準諧振反激形式應用中,由于MOS導通時的電壓較高(基本都在150V以上),特別是高壓的輸入條件下,會有較高的開關損耗及DI/Dt造成的EMI干擾,影響系統效率及EMI特性。直到ZVS反激式電路的出現,很好的解決了這些痛點。

先從反激應用電路開始分析,再轉到ZVS零電壓開關電路應用

一. 反激應用中MOSFET的損耗分析

MOSFET的損耗主要包括如下幾個部分:

1. 導通損耗

導通損耗是比較容易理解的,即流過MOSFET的RMS電流在MOSFET的Rdson上的I^2R損耗。降低這個損耗也是大家最容易想到的,例如選用更低Rdson的管子,設計變換器進入更深的連續模式來降低RMS電流等。然而需要注意的是,Rdson和Q互相矛盾,最終,只能在兩者之間找到一個平衡點。

2. 關斷損耗

關斷損耗即MOSFET在關斷狀態下,流過MOSFET的漏電流和MOSFET承受的電壓之積。通常這項損耗是大家忽略的,實際上也是完全可以忽略的。例如一個耐壓600V左右的MOSFET,即便在150°C下,漏電流也僅僅是uA級的,帶來的損耗也僅僅是mW級的。

3. 開關損耗

開關損耗包括開通損耗和關斷損耗。開通損耗指的是MOSFET開通期間Ids上升和Vds下降交叉面積帶來的損耗;關斷損耗指的是MOSFET關斷期間Ids下降和Vds上升交叉面積帶來的損耗。

不論是開通損耗還是關斷損耗,主要是發生在米勒電容放電或者充電區間,即決定開關損耗的主要是米勒平臺的時間以及開關頻率。

對于目前的反激式應用,由于開關頻率普遍偏低(絕大多數低于100KHz),并且高壓輸入下CCM的深度很淺(對于全電壓工作的電源,絕大多數低壓CCM工作的,高壓基本上工作于DCM或非常接近DCM),同時加上MOSFET的進步(CoolMOS和Super Junction大大降低了Crss),實際應用中MOSFET的開通損耗是比較小的。拿一個使用CoolMOS或Super Junction MOSFET的電源,驅動開通電阻從幾歐到幾十歐甚至上百歐變動,效率幾乎不受影響。

由于反激原邊MOSFET關斷發生在[敏感詞]電流處,因此關斷損耗通常比較可觀。為了降低關斷損耗,通常從加快關斷速度上想辦法。

4. 容性損耗

這里把容性損耗獨立于開關損耗來討論。容性損耗指的是MOSFET開通瞬間,DS間寄生電容通過MOSFET DS直接放電產生的損耗。我們經常可以看到原邊電流波形并非一個理想的三角形或梯形,而是在開通瞬間存在一個電流尖峰,導致峰值電流控制模式的IC不得不做前沿消隱。

從一個MOSFET的規格書中,通常可以看到兩個可以用來直接估算容性損耗的參數,Eoss和Co(er)。拿英飛凌[敏感詞]一代的CoolMOS IPD70R360P7S舉例:Eoss@400V=1.8uJ,Co(er)=27pF(Vds=0~400V)

如果把Co(er)乘以Vds(400V)的平方再除以2,得到能量2.16uJ,和Eoss基本一致。

比較簡單的估算,如果開關頻率f=100KHz,則Vds=400V下的容性損耗約:Pco=Eoss*f=0.18W

在實際應用中,這個損耗很可能是被低估的,有如下原因:

首先實際應用中,264VDC輸入下,輸入直流電壓374V,如果反射電壓100V,那開通瞬間的Vds電壓可能在374-100=274V(QR)到374+100=474V之間,即實際的Eoss可能大于或者小于規格書給出的值;

其次實際應用中,MOSFET的DS間等效電容不僅包含MOSFET本身電容,還有變壓器寄生電容,后者很可能大于前者,這種情況下,實際Eoss損耗會遠大于計算值。

5. 驅動損耗

驅動損耗即Ciss的充放電損耗,計算方法如下:

Pdrv=Qg*Udrv*f

通常應用下也被忽略,一方面由于MOSFET的進步,Qg有了顯著的降低,一方面頻率比較低。例如IPD70R360P7S,Qg=16.4nC(Vgs=0~10V,Vds=400V),驅動電壓10V,工作頻率100K下,驅動損耗僅為:

Pdrv=16.4*10*100/1000=16.4mW

需要注意的是,與前面幾項損耗不同,驅動損耗雖然是MOSFET的結電容充放電導致的,但絕大部分沒有損耗在MOSFET上,而是損耗在驅動IC和驅動電阻上。

二. ZVS的實現方案

ZVS即在MOSFET驅動到來前,Vds電壓已經為零了。由于節點電容上電壓的存在,要實現ZVS,需要一個和勵磁電流反向的電流流過變壓器原邊電感。傳統的QR,由于退磁后變壓器初級電感的初始電壓即副邊反射電壓,振蕩是阻尼的,因此開關節點可能達到的[敏感詞]電壓只能是Vin-Vor,能不能ZVS取決于輸入電壓和反射電壓。對于寬范圍輸入,不太可能全輸入范圍實現ZVS;如果再加上寬范圍輸出(比如PD協議5-20V輸出的適配器),ZVS的實現就愈發困難。

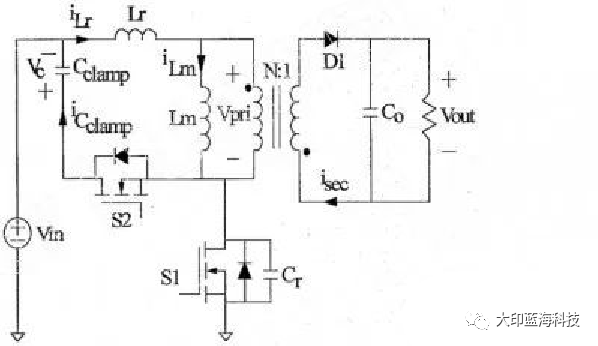

為了實現這個反向的電流,對電感而言,只需對它反向勵磁,有源鉗位反激就是這樣一個思路。

相對于傳統反激,有源鉗位反激中RCD吸收不可控導通的D變成了可控導通的MOSFET,鉗位電容容值遠大于吸收電容。漏感能量存儲在鉗位電容中,在鉗位電容上形成一個相對平穩的電壓。在原邊主MOSFET開通前,如果先將鉗位管開通一段時間,原邊電感將反向勵磁,關斷鉗位管后,勵磁電流方向不變,這個電流抽取結電容電荷,最后實現主MOSFET的ZVS。

有源鉗位的好處是不僅實現了ZVS,同時能夠回收漏感能量,但從電路結構上,增加了一顆高邊鉗位管,控制IC需要高壓浮區,成本大幅上升。

本文要討論的ZVS反激,講的是不改變傳統反激電路基本結構,不增加額外的器件,僅從控制上想辦法來實現。

前面提到,為了實現ZVS,需要在原邊管開通前,在原邊電感上形成原邊一個負電流,即原邊電感需要反相勵磁。ACF根本方法就是在原邊電感上直接反相勵磁,代價是必須增加一個可控開通和關斷MOSFET。

對于Flyback,變壓器本質上是一個耦合電感,要在原邊電感形成負電流,這反相勵磁其實是可以從任一繞組上來操作的,因為關斷后,能量可以從任一繞組釋放。基于這個原理,ZVS的實現就變得相當簡單了。試想一下,工作在DCM下,帶有有同步整流的Flyback,如果副邊退磁完成后同步整流繼續保持開通,那么輸出電壓將會從輸出繞組對變壓器勵磁,只要在原邊開通前一定時間內關斷同步整流,變壓器內存儲的能量就會尋找途徑釋放,而此時,它就會反抽原邊開關節點電容形成負電流,只要勵磁能量足夠,反抽時間(同步整流關斷到原邊開通的死區時間)合適,就能確保零電壓開通。

當然,勵磁可以在變壓器上其他任何一個耦合的繞組上進行。

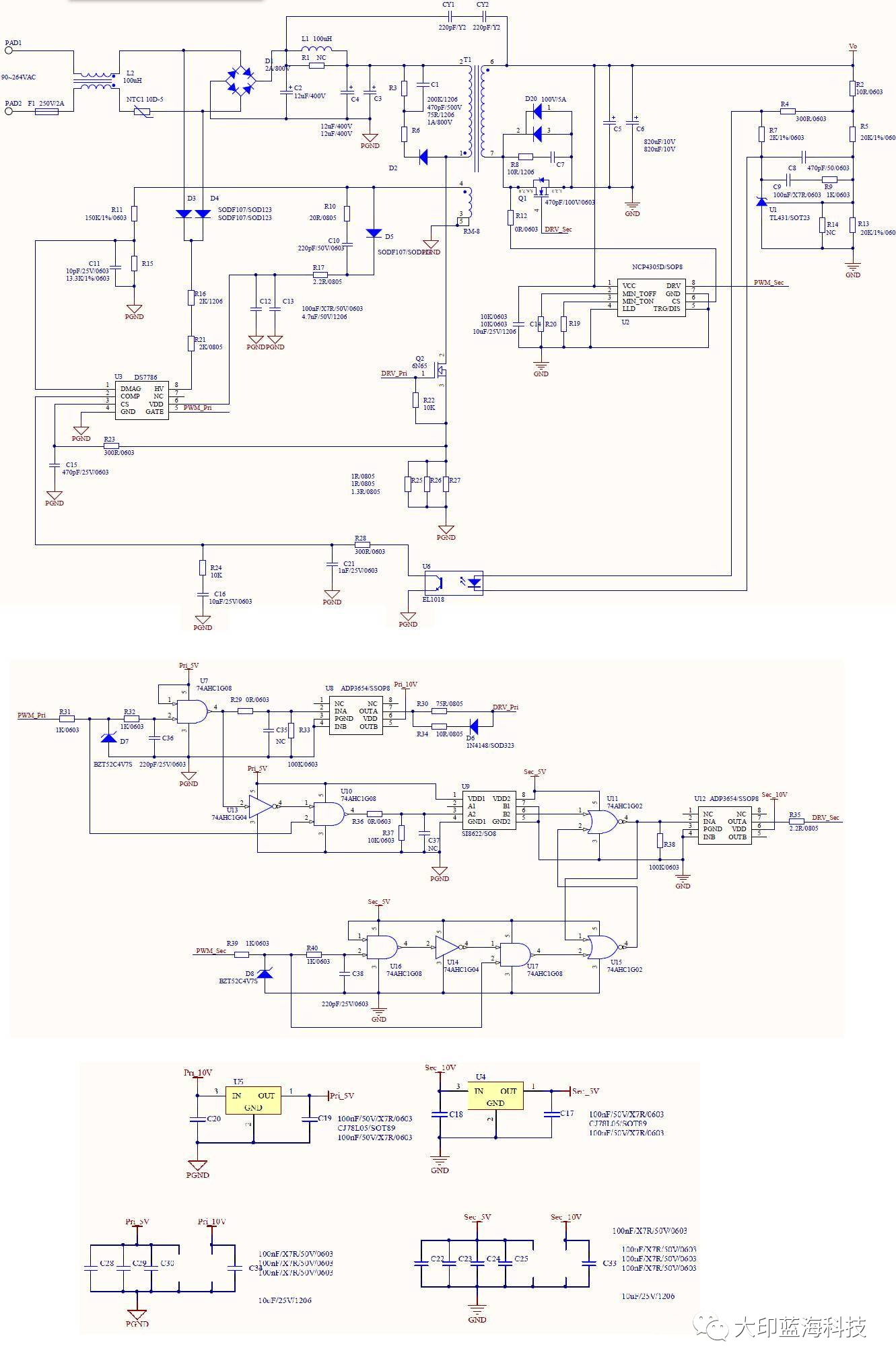

先上[敏感詞]個原理圖,是我前兩年搭的一個實驗電路,用一個定頻PWM控制器配合一些數字邏輯電路,實現同步整流與原邊驅動的互補輸出,同時留有死區,這個電路經過驗證,DCM下可以從副邊同步整流倒灌,實現原邊零電壓開通。至于原理,相信大家仔細看看都能理解。

這種方案有一個很大的問題,注入的能量損耗可能遠超過ZVS帶來的收益。

同步整流如果與原邊完全互補,那深度DCM下,反灌到變壓器的能量可能遠大于原邊結電容存儲能量,較大的能量在一來一回中損失了。接下來上另一個圖,這種實現非互補的驅動,只是在原邊開通前打出一個小脈沖,不多不少,正好能夠抽干結電容能量就好。

三. 國產ZVS芯片

說到ZVS(零電壓開關技術)反激,相信大家并不陌生,早在2018年,華為在mate20發布會上推出的40W SuperCharge超級快充充電器,就采用了英飛凌ZVS反激快充方案,這也是ZVS反激的首次商用,該方案具有小體積、大功率、高效率等特點,有效的提高了產品效率及功率密度,因而在華為旗艦機標配超級快充中一直被沿用。

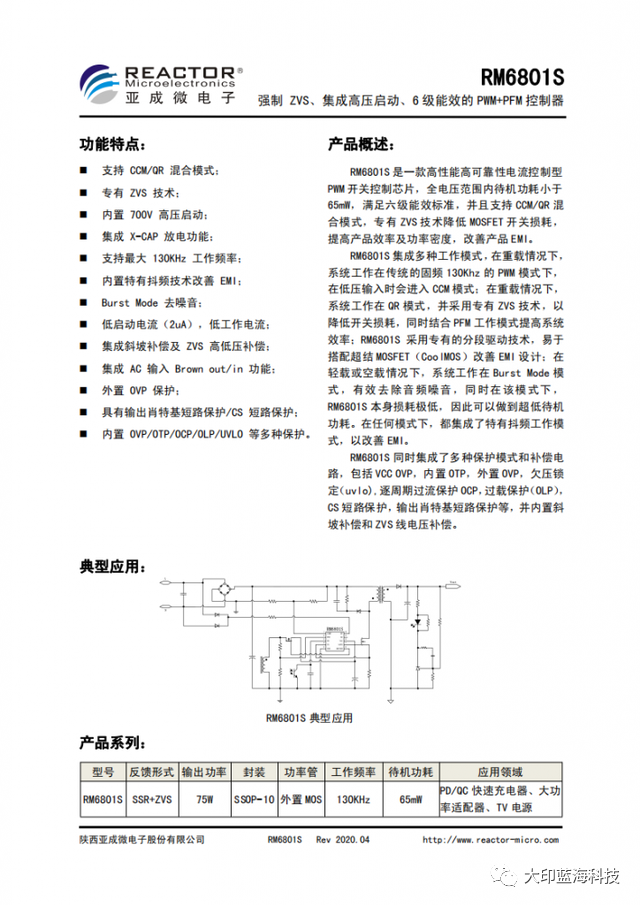

而作為一家國內領先的模擬IC設計公司,亞成微電子于近期成功推出了國內[敏感詞]ZVS反激式開關電源芯片RM6801S,填補了國內空白。RM6801S是一款高性能高可靠性電流控制型PWM開關控制芯片,內置700V高壓啟動,X-cap放電,可調交流輸入Brown in/out等功能,工作頻率高達130Khz,全電壓范圍內待機功耗小于65mW,滿足六級能效標準,并且支持CCM/QR混合模式以及擁有完備的各種保護功能,專有ZVS技術降低MOSFET開關損耗,改善EMI特性。采用分段驅動技術,搭配超結MOSFET(CoolMOS),并兼容直驅E-MODE GaN功率器件版本,提高產品效率及功率密度,簡化EMI濾波電路設計,降低EMI器件成本,完美應用于大功率快速充電器。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號