服務熱線

0755-83044319

發布時間:2023-03-10作者來源:印寧華瀏覽:4421

三星在年初的IEEE國際固態電路大會(ISSCC)上,公布3nm制造技術的一些細節,包括類似全柵場效應晶體管(GAAFET)結構,率先開啟先進工藝在技術架構上的轉型。知名能源與電力媒體eenews報道稱,三星工廠已經流片采用環繞柵極 (GAA) 晶體管架構的3nm芯片,通過納米片(Nanosheet)制造出MBCFET(多橋通道場效應管),可顯著增強晶體管性能,主要取代FinFET晶體管技術。

為了能夠從臺積電手中搶到客戶,三星半導體最近幾年一直在積極宣傳GAA(Gate All Around)。伴隨著成功流片,三星3nm芯片即將進入模量產。但隨后有消息稱,可能在2022年推出的3nm(GAA架構),要推遲到2024年。

根據三星官方的數據,7nm FinFET制造工藝相比,3nm GAA技術的邏輯面積效率提高35%以上,功耗降低50%,邏輯面積減少45%。三星執行副總裁兼代工銷售和營銷主管Charlie Bae表示:“基于GAA結構的下一代工藝節點(3nm)將使三星能夠率先打開一個新的智能互聯世界,同時加強我們的技術領先地位”。

什么是GGA晶體管?

GGA的全稱是Gate All Around Field Effect Transistors(簡稱GAAFET),中文全稱全環柵晶體管,能夠延續半導體技術經典“摩爾定律”的新興技術路線,可進一步增強柵極控制能力,克服當前技術的物理縮放比例和性能限制。

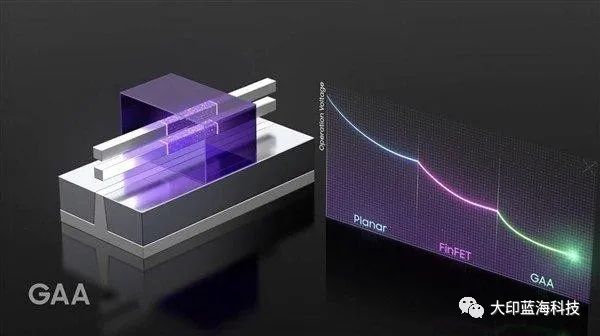

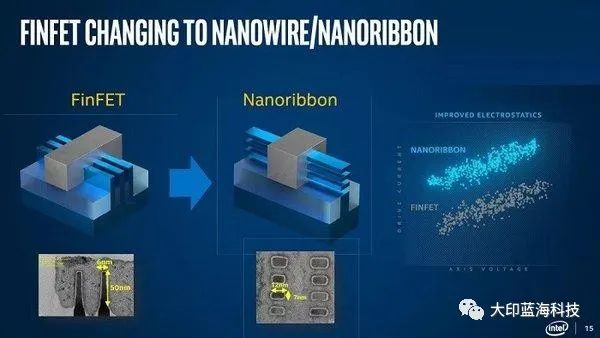

GAAFET有兩種結構,一種是使用納米線(Nanowire)作為電子晶體管鰭片的常見GAAFET;另一種則是以納米片(Nanosheet)形式出現的較厚鰭片的多橋通道場效應管MBCFET,這兩種方式都可以實現3nm工藝節點,只是取決于制造商具體的設計。從GAAFET到MBCFET,可以視為從二維到三維的躍進,能夠改進電路控制,降低漏電率。

GAA晶體管能夠提供比FinFET更好的靜電特性,滿足某些柵極寬度的需求。在同等尺寸結構下,GAA溝道控制能力增強,給尺寸進一步微縮提供可能;傳統FinFET的溝道僅三面被柵極包圍,GAA以納米線溝道設計的整個外輪廓都被柵極完全包裹,意味著柵極對溝道的控制性能就更好。Leti公司高級集成工程師Sylvain Barraud指出:“與FinFET相比,除了具有更好的柵極控制能力以外,GAA堆疊的納米線還具有更高的有效溝道寬度,能夠提供更高的性能。”

臺積電與三星的分歧

臺積電和三星在5nm、7nm節點繼續使用FinFET(鰭式場效應管)結構,但是3nm工藝的晶體管結構選擇出現分歧。三星確認將率先在3nm的工藝節點上使用GAAFET,臺積電則更保守的使用FinFET結構。只是臺積電使用FinFET工藝知識權宜之計,工藝制程來到3nm之后,鰭片(Fin)寬度達到5nm(等于3nm節點)時,FinFET將接近實際極限,再向下就會遇到瓶頸。

因此,有消息稱臺積電也將在2nm工藝節點將轉向GAA架構,全新的MBCFET架構以GAA制程為基礎,可以解決FinFET因為制程微縮而產生的電流控制漏電等物理極限問題。2nm或將是FinFET結構全面過渡到GAA結構的技術節點。在經歷了Planar FET、FinFET后,晶體管結構將整體過渡到GAAFET結構上。

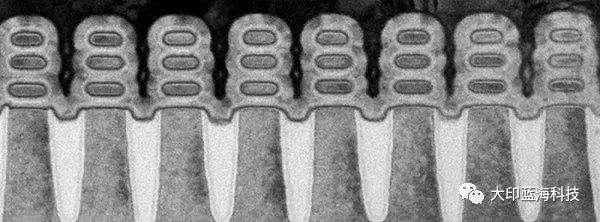

臺積電選擇在[敏感詞]代3nm工藝繼續使用FinFET技術,處于多方面的考慮。首先是相同的制程技術與制造流程下,無需不用變動太多的生產工具,就能實現從FinFET切換到GAA,具有不錯的成本優勢。特別是先進工藝晶圓的設計成本,會讓客戶更加謹慎的選擇制造工藝。根據早前曝光的設計奮勇來看,5nm的晶圓開發費用高達4.76億美元,3nm甚至2nm只會更高。

在先進制程的開發里變更設計,無論是改變設計工具或者是驗證和測試的流程,都會是龐大的時間和經濟成本,幫助客戶降低生產的成本。。臺積電首席科學家黃漢森強調,選擇FinFET工藝是從客戶角度出發的,成熟的FinFET結構產品性能會更加穩定。

三星方面,最近幾年的晶圓制造出與追趕階段,他們需要在3nm時代尋找技術架構差異化,拉近與臺積電芯片代工方面的技術差距,用更激進的策略來獲取客戶的青睞。IBS首席執行官Jones表示:“與3nm FinFET相比,3nm環繞閘極具有更低的閾值電壓,可能帶來15%到20%的功耗降低,在某種程度上提供更多的性能。”

未來晶體管結構

市場對于高性能芯片的渴望在不斷推動技術的進步,新的GAA技術讓3nm節點工藝成為現實。但是在GAA之后,半導體又有可能往哪些方向發展?

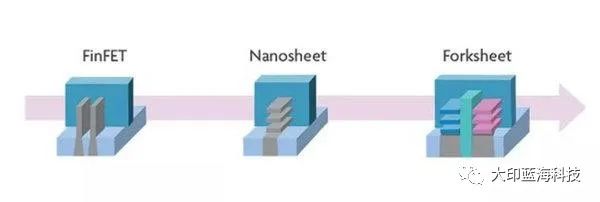

Forksheet FET

隨著未來向更小制程的繼續,將要求標準單元內nFET和pFET器件之間的間距更小。但FinFET和Nanosheet的工藝限制n-to-p器件之間的間距。除了Nanosheet,還有一些屬于“全柵”類的其它技術選項。為了擴大這些器件的可微縮性,IMEC提出一種創新的架構,稱為Forksheet FET。

Forksheet可以理解為是Nanosheet的自然延伸,具有超出2nm技術節點的額外縮放和性能。Forksheet的nFET和pFET集成在同一結構中,由介電墻將nFET和pFET隔開。優勢在于它有更緊密的n到p的間距,并減少面積縮放。與Nanosheet FET相比,在相同制程下的Forksheet FET電路將更加緊湊。

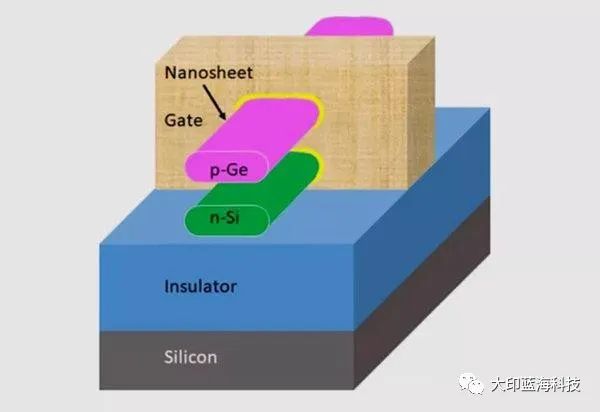

在從平面晶體管到FinFET再到Nanosheet的進化過程中,可以將Forksheet視為下一個發展路徑。CFET(Complementary FETs,互補場效應晶體管)是2nm甚至以后另一種類型的技術選項,由兩個獨立的Nanosheet FET(p型和n型)組成,把p型納米線疊在n型納米線上的結構。通過疊加的方式實現折疊的,借此消除n-to-p分離的瓶頸,能夠將單元有源區域的面積減少2倍。

IBS首席執行官Handel Jones稱:“CFET前景廣闊,但目前還為時過早。向1nm CFET系列邏輯器件的發展推動新BEOL和MOL解決方案的開發,但問題是即使增強了柵極結構,我們也需要增強MOL和BEOL,需要通過引入新的導體來補充這些集成方案,否則性能提升將受到限制。”對于未來技術架構的演進趨勢,IMEC認為:3納米之前采用Nanosheet、2納米采用Forksheet、1納米采用CFET。

在進一步的研究中,需要解決將這些器件完全投入生產的工藝挑戰。目前這些仍在研發中的技術前景尚好,但也都有更自的挑戰待突破,包含散熱的控制和制造成本等。但可以看到的是,2納米及之后已有數項技術正在進行中,雖有困難但也是遙不可及。

Bizen晶體管架構

英國初創公司Search For The Next(SFN)和蘇格蘭芯片制造商Semefab合作開發Bizen晶體管架構,可能從另一方向打破CMOS的極限。提出Bizen晶體管架構最初的目的就是為了創建具有較少掩膜步驟的芯片,使得同一塊芯片上同時具有邏輯和功率晶體管,在這一初衷下創建一個LED驅動器的集成電路。

SFN首席執行官Summerland提出使用齊納二極管反向偏置特性的想法,該特性是由二極管N區域和P區域之間摻雜水平的突然變化產生的,最終致使量子電流的產生,以此來驅動雙極晶體管。SFN的Bizen晶體管設計將雙極結與齊納二極管的概念結合在一起,利用量子隧穿效應從傳統的雙極晶體管中消除了電阻以及所有金屬層。晶體管使用量子隧道連接柵極并能夠建立多個柵極連接,這意味著可以在一個晶體管內創建多個非門和或門,從而縮小了邏輯電路的裸片。

由于沒有能夠滿足所有應用的技術,在芯片微縮和功能擴展的過程中,制程的進步、晶體管結構的變化和其他方法會交替進行,不斷推動芯片性能提升。在先進半導體制造的成本不斷攀升的當下,如何利用現有的技術,獲得客戶青睞至關重要;如果芯片制造商不能在生產技術與制造成本中取得較好的平衡,未來難以在競爭中保持優勢地位。

免責聲明:本文原創作者印寧華,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號