服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2022-03-18作者來源:薩科微瀏覽:3133

關(guān)于差分輸入、PGA和儀表放大器及混合SOC設(shè)計(jì),最近整理一些交流心得分享

下面是微群里的聊天記錄

之前群里交流的內(nèi)容多數(shù)還是在應(yīng)用市場和商務(wù)MARCON上. 不妨換個(gè)角度,聊聊芯片內(nèi)部的話題, 比如SOC, AFE, MCU 低功耗的設(shè)計(jì).

針對于數(shù)字和模擬芯片設(shè)計(jì)者,大家對一款通用器件的理解和出發(fā)點(diǎn)是不一樣的。比如, 可能大家對儀表放大器理解的角度就會有所不同吧,將差分輸入,MUX, BUFFER, PGA Gain都合起來可稱為儀放功能再后級加ADC就算是AFE的概念了吧 不過將AFE+MCU集成為SOC的方式目前看起來還是以合封的方式為多。

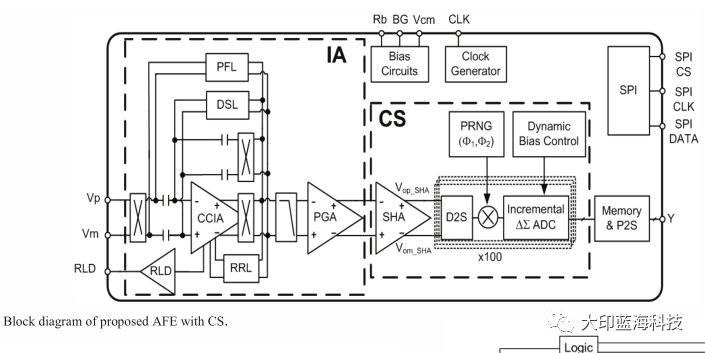

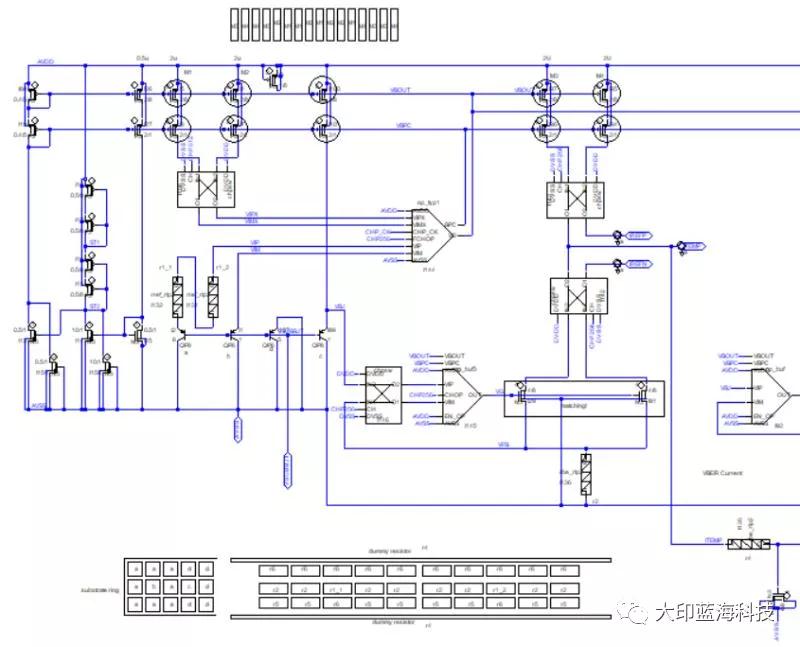

一種帶有儀放(Instrumentation Amplifier - IA)

壓縮感知(Compressed Sensing -CS)的SOC內(nèi)部框圖

IA- Instrument Amplfiier (也有人簡稱為INA) , 對于獨(dú)立的儀表放大器,HPA公司會認(rèn)為主要的功能是高Vcm, 高CMRR/PSRR,高的開環(huán)增益,以及盡可能低的Vos。

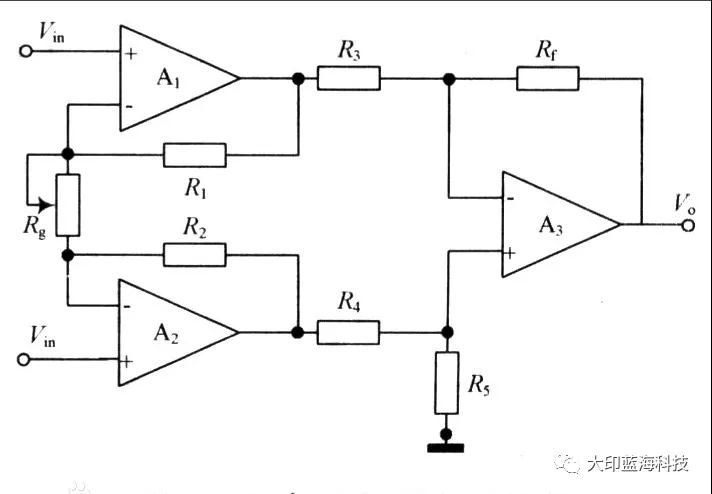

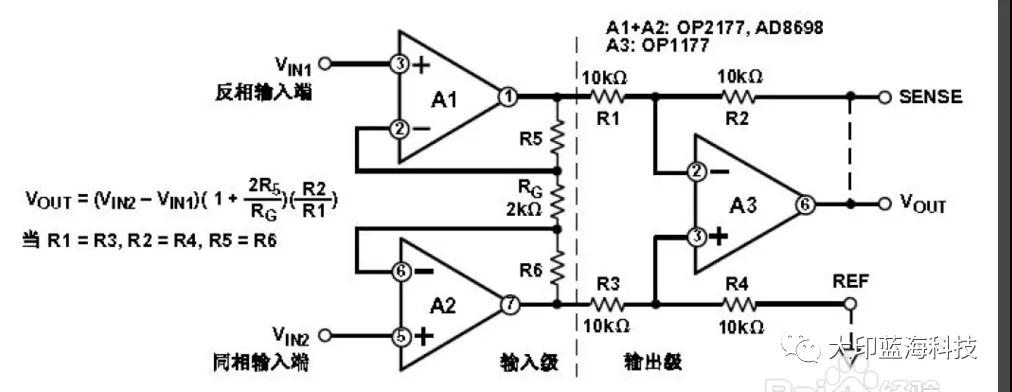

儀表放大器電路的典型結(jié)構(gòu)如下圖所示。它主要由兩級差分放大器電路構(gòu)成。其中,運(yùn)放A1,A2為同相差分輸入方式,同相輸入可以大幅度提高電路的輸入阻抗,減小電路對微弱輸入信號的衰減;差分輸入可以使電路只對差模信號放大,而對共模輸入信號只起跟隨作用,使得送到后級的差模信號與共模信號的幅值之比(即共模抑制比CMRR)得到提高。這樣在以運(yùn)放A3為核心部件組成的差分放大電路中,在CMRR要求不變情況下,可明顯降低對電阻R3和R4,Rf和R5的精度匹配要求,從而使儀表放大器電路比簡單的差分放大電路具有更好的共模抑制能力。在R1=R2,R3=R4,Rf=R5的條件下,圖1電路的增益為:G=(1+2R1/Rg)Rf/R3。由公式可見,電路增益的調(diào)節(jié)可以通過改變Rg阻值實(shí)現(xiàn)。

特性包括非常低直流偏移、低漂移、低噪聲、非常高的開環(huán)增益、非常大的共模抑制比、高輸入阻抗。儀表放大器用于需要精確性和穩(wěn)定性非常高的電路。

雖然儀表放大器在線路圖上是一顆運(yùn)算放大器;但實(shí)際上是由三顆運(yùn)算放大器所組成(如圖一所示);儀表放大器分成兩個(gè)部分,輸入端的兩個(gè)電壓跟隨器提供輸入端(+,?)高輸入阻抗,后級則是差分放大器,用來做兩個(gè)輸入端的差分放大;不過,通常第二級的差分放大器的增益會設(shè)計(jì)為1,也就是只做兩個(gè)電壓的相減運(yùn)算。

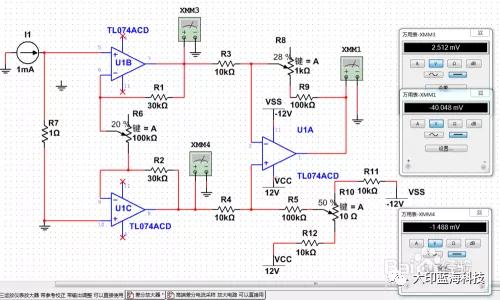

實(shí)用的三運(yùn)放組成的儀表放大器仿真測試電路

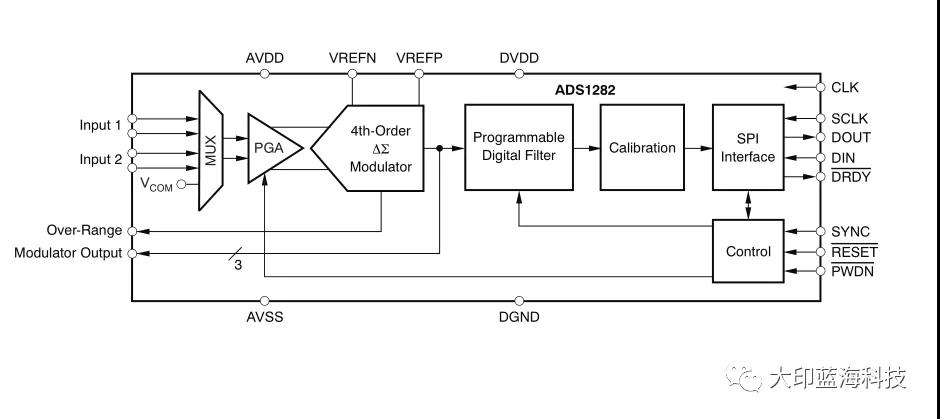

除了常見到的獨(dú)立運(yùn)放組成的專用INA儀放,我們還常在ADC內(nèi)部電路中見到差分輸入+PGA類似儀表的組合

一款典型的TI-ADS1282 32bit Ultra Delta-Sigma ADC

內(nèi)置全差分輸入 Mux TIA Buffer +PGA

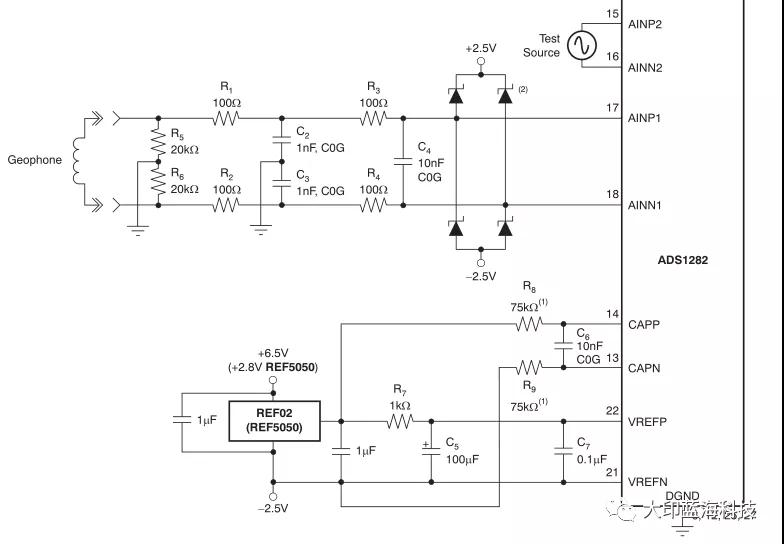

ADS1282配合外置Vref正負(fù)基準(zhǔn)電壓的外部接線示意圖

關(guān)于壓縮感知CS

一、什么是壓縮感知(CS)?

compressed sensing又稱compressed sampling,似乎后者看上去更加直觀一些。沒錯(cuò),CS是一個(gè)針對信號采樣的技術(shù),它通過一些手段,實(shí)現(xiàn)了“壓縮的采樣”,準(zhǔn)確說是在采樣過程中完成了數(shù)據(jù)壓縮的過程。

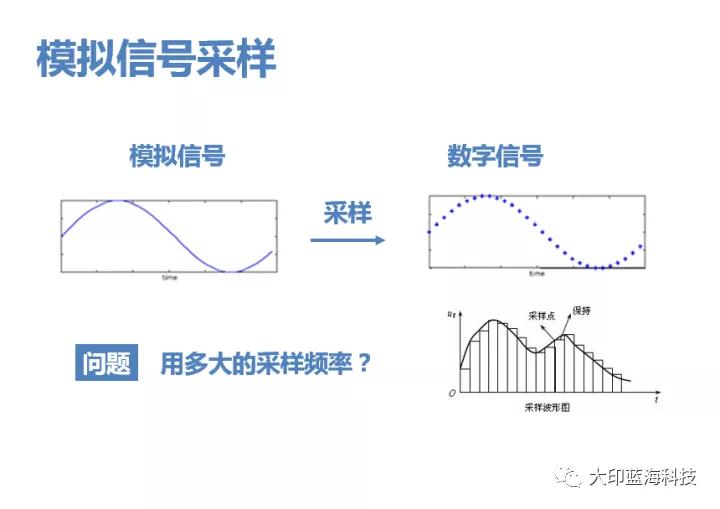

因此我們首先要從信號采樣講起:

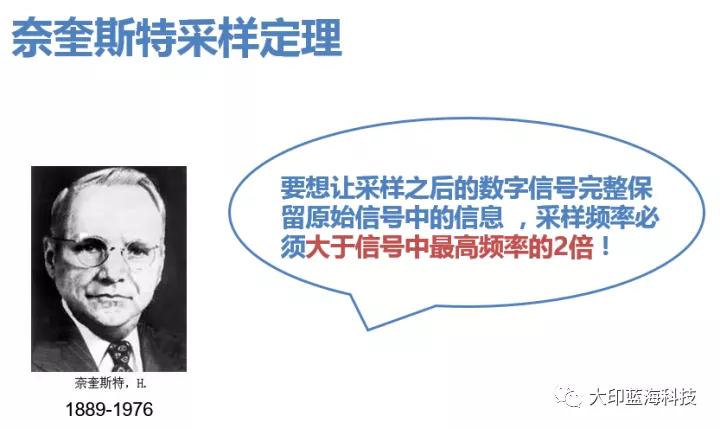

1. 我們知道,將模擬信號轉(zhuǎn)換為計(jì)算機(jī)能夠處理的數(shù)字信號,必然要經(jīng)過采樣的過程。問題在于,應(yīng)該用多大的采樣頻率,即采樣點(diǎn)應(yīng)該多密多疏,才能完整保留原始信號中的信息呢?

---------------------------------------

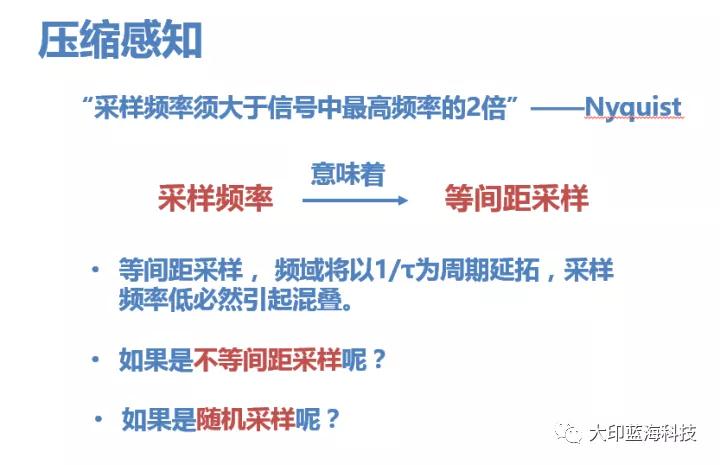

2. 奈奎斯特給出了答案——信號[敏感詞]頻率的兩倍。一直以來,奈奎斯特采樣定律被視為數(shù)字信號處理領(lǐng)域的金科玉律。

---------------------------------------

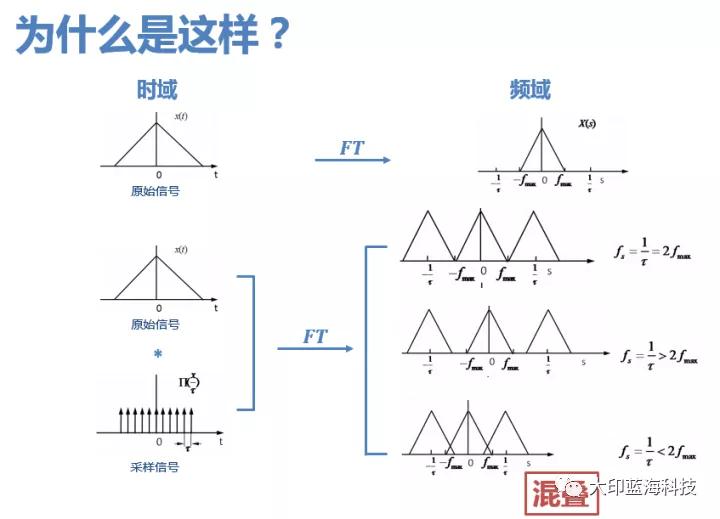

3. 至于為什么是兩倍,學(xué)過信號處理的同學(xué)應(yīng)該都知道,時(shí)域以τ為間隔進(jìn)行采樣,頻域會以1/τ為周期發(fā)生周期延拓。那么如果采樣頻率低于兩倍的信號[敏感詞]頻率,信號在頻域頻譜搬移后就會發(fā)生混疊。

---------------------------------------

4. 然而這看似不容置疑的定律卻受到了幾位大神的挑戰(zhàn)。Candes最早意識到了突破的可能,并在不世出的數(shù)學(xué)天才陶哲軒以及Candes的老師Donoho的協(xié)助下,提出了壓縮感知理論,該理論認(rèn)為:如果信號是稀疏的,那么它可以由遠(yuǎn)低于采樣定理要求的采樣點(diǎn)重建恢復(fù)。

---------------------------------------

5. 而突破的關(guān)鍵就在于采樣的方式。當(dāng)我們說“采樣頻率”的時(shí)候,意味著做的是等間距采樣,數(shù)字信號領(lǐng)域通常都是做等間距采樣,也服從奈奎斯特采樣定律。

但是如果是不等間距采樣呢?依然必須要服從采樣定理嗎?

---------------------------------------

6. 答案是,隨機(jī)的亞采樣給了我們恢復(fù)原信號的可能。

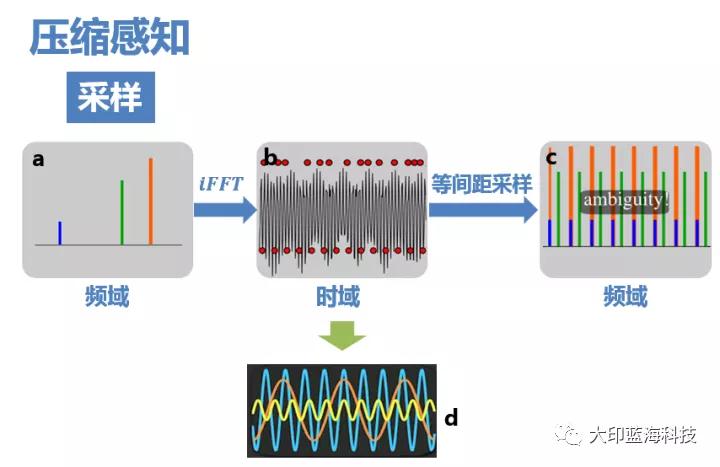

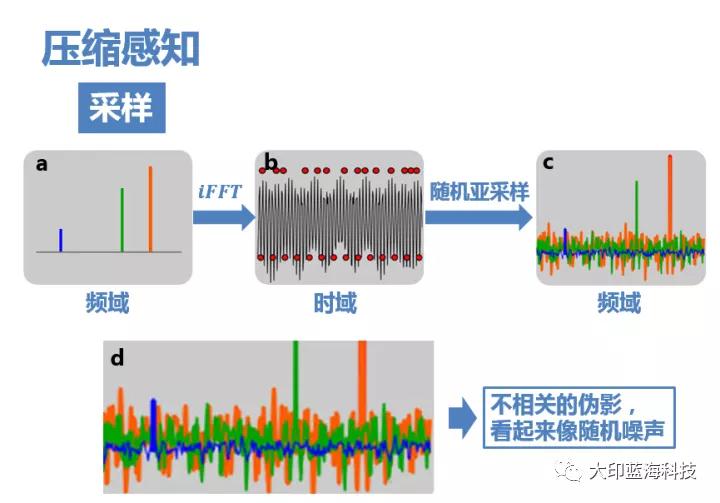

上圖非常關(guān)鍵,它可以簡單直觀地表述壓縮感知的思路。如圖b、d為三個(gè)余弦函數(shù)信號疊加構(gòu)成的信號,在頻域的分布只有三條線(圖a)。如果對其進(jìn)行8倍于全采樣的等間距亞采樣(圖b下方的紅點(diǎn)),則頻域信號周期延拓后,就會發(fā)生混疊(圖c),無法從結(jié)果中復(fù)原出原信號。

---------------------------------------

7. 而如果采用隨機(jī)亞采樣(圖b上方的紅點(diǎn)),那么這時(shí)候頻域就不再是以固定周期進(jìn)行延拓了,而是會產(chǎn)生大量不相關(guān)(incoherent)的干擾值。如圖c,[敏感詞]的幾個(gè)峰值還依稀可見,只是一定程度上被干擾值覆蓋。這些干擾值看上去非常像隨機(jī)噪聲,但實(shí)際上是由于三個(gè)原始信號的非零值發(fā)生能量泄露導(dǎo)致的(不同顏色的干擾值表示它們分別是由于對應(yīng)顏色的原始信號的非零值泄露導(dǎo)致的)

P.S:為什么隨機(jī)亞采樣會有這樣的效果?

這可以理解成隨機(jī)采樣使得頻譜不再是整齊地搬移,而是一小部分一小部分胡亂地搬移,頻率泄露均勻地分布在整個(gè)頻域,因而泄漏值都比較小,從而有了恢復(fù)的可能。

---------------------------------------

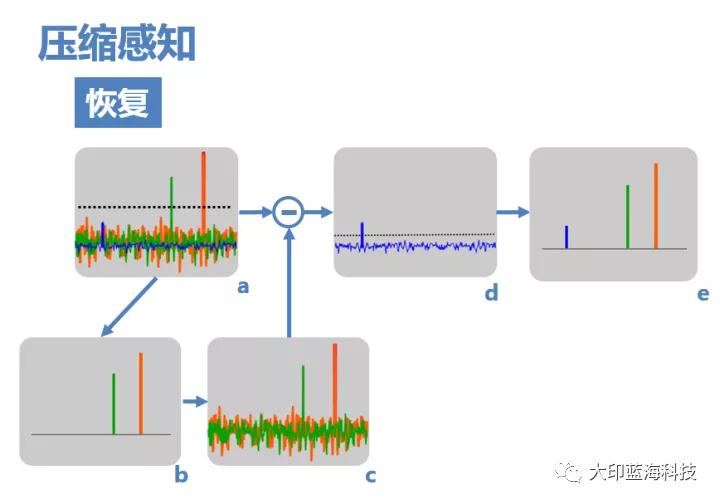

8. 接下來的關(guān)鍵在于,信號該如何恢復(fù)?下面講一種典型的算法(匹配追蹤):

(1) 由于原信號的頻率非零值在亞采樣后的頻域中依然保留較大的值,其中較大的兩個(gè)可以通過設(shè)置閾值,檢測出來(圖a)。

(2) 然后,假設(shè)信號只存在這兩個(gè)非零值(圖b),則可以計(jì)算出由這兩個(gè)非零值引起的干擾(圖c)。

(3) 用a減去c,即可得到僅由藍(lán)色非零值和由它導(dǎo)致的干擾值(圖d),再設(shè)置閾值即可檢測出它,得到最終復(fù)原頻域(圖e)

(4) 如果原信號頻域中有更多的非零值,則可通過迭代將其一一解出。

以上就是壓縮感知理論的核心思想——以比奈奎斯特采樣頻率要求的采樣密度更稀疏的密度對信號進(jìn)行隨機(jī)亞采樣,由于頻譜是均勻泄露的,而不是整體延拓的,因此可以通過特別的追蹤方法將原信號恢復(fù)。

二、壓縮感知的前提條件

接下來我們總結(jié)一下,能實(shí)現(xiàn)壓縮感知的關(guān)鍵在于什么,即需要哪些前提條件。

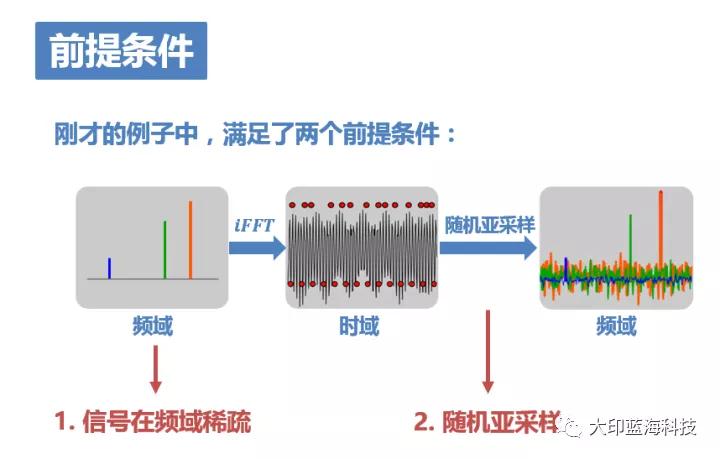

9. 在剛才的講述中大家可以感受到,這個(gè)例子之所以能夠?qū)崿F(xiàn)最終信號的恢復(fù),是因?yàn)樗鼭M足了兩個(gè)前提條件:

1. 這個(gè)信號在頻域只有3個(gè)非零值,所以可以較輕松地恢復(fù)出它們。

2. 采用了隨機(jī)亞采樣機(jī)制,因而使頻率泄露均勻地分布在整個(gè)頻域。

這兩點(diǎn)對應(yīng)了CS的兩個(gè)前提條件——稀疏性(sparsity)、不相關(guān)性(incoherence)

---------------------------------------

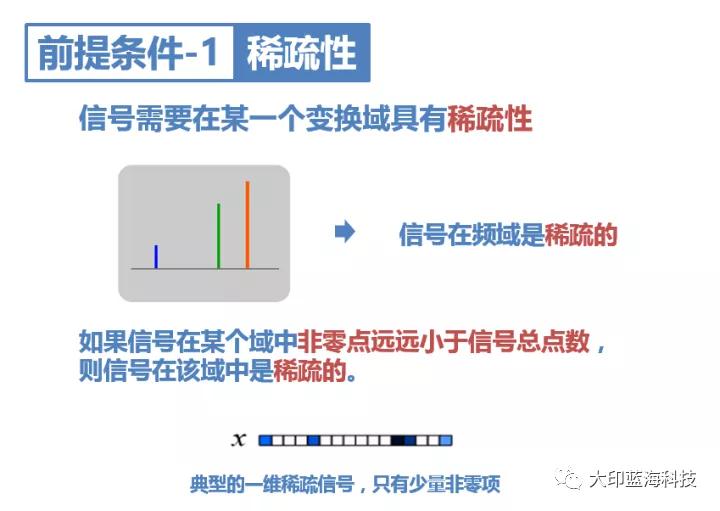

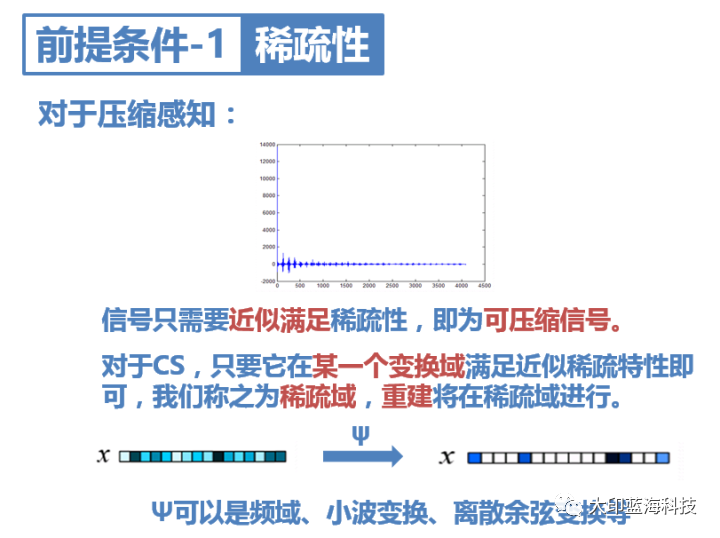

10. 關(guān)于稀疏性可以這樣簡單直觀地理解:若信號在某個(gè)域中只有少量非零值,那么它在該域稀疏,該域也被稱為信號的稀疏域。

因此,[敏感詞]個(gè)前提條件要求信號必須在某一個(gè)變換域具有稀疏性。比如例子中,信號在頻域是稀疏的,因而可以通過所述的重建方法輕松地在稀疏域(頻域)復(fù)原出原信號。

---------------------------------------

然而通常信號在變換域中不會呈現(xiàn)完全的稀疏性。其實(shí)只要它近似滿足稀疏性,即大部分值趨于零,只有少量大的非零值,就可以認(rèn)為它是可壓縮信號,可以對它進(jìn)行CS亞采樣。

對于之前講的例子,如果它在頻域中不稀疏,我們可以做DWT、DCT等,找到它的稀疏變換。

---------------------------------------

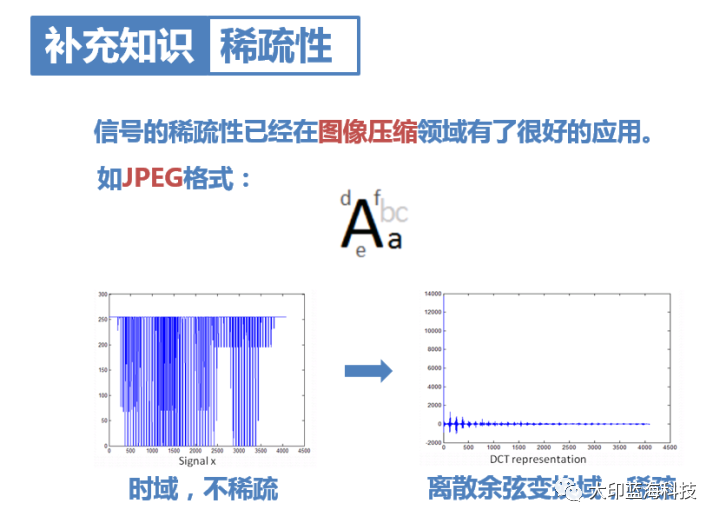

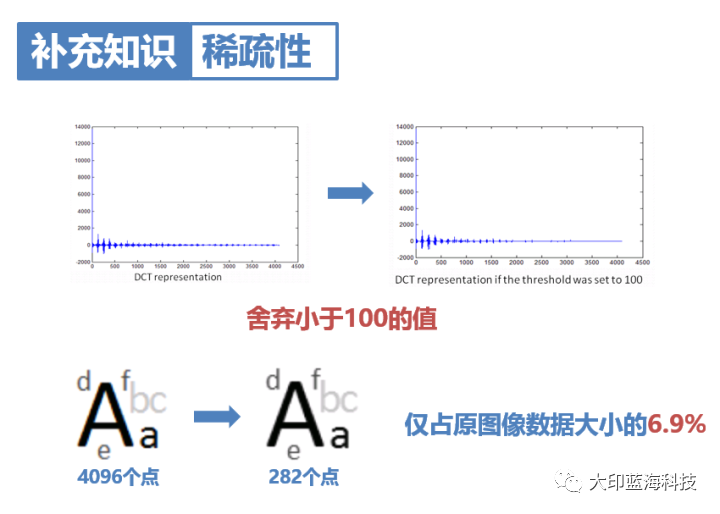

11. 這里針對信號的稀疏性和信號壓縮額外補(bǔ)充一下:其實(shí),信號的稀疏性已經(jīng)在圖像壓縮領(lǐng)域有了很廣泛的應(yīng)用。利用信號的稀疏性,可以對信號進(jìn)行壓縮。如圖像壓縮領(lǐng)域的JPEG格式,就是將圖像變換到離散余弦域,得到近似稀疏矩陣,只保留較大的值,從而實(shí)現(xiàn)壓縮。

---------------------------------------

12. 比如這個(gè)例子中,僅用原圖像6.9%的點(diǎn)就復(fù)原了和原圖像基本相同的圖像。我們還可以采用小波變換,即為JPEG-2000,壓縮效果更好。

---------------------------------------

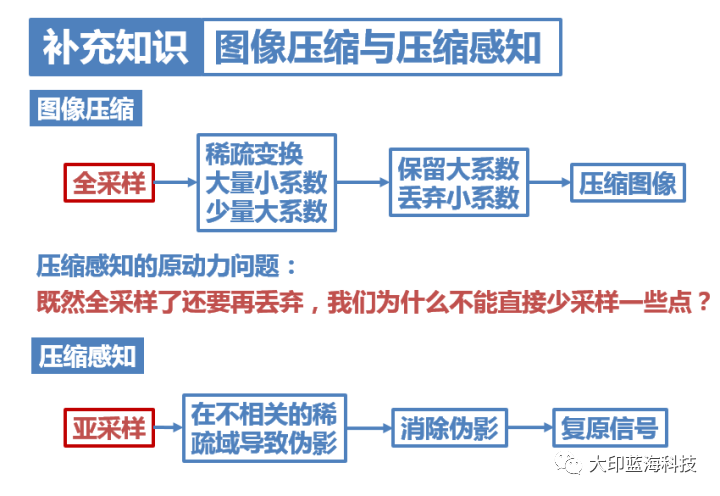

13. 這里需要指出,圖像壓縮和壓縮感知這兩個(gè)概念很容易弄混,大家一定要分清。

它們其實(shí)有著本質(zhì)上的區(qū)別。圖像壓縮是先進(jìn)行了全采樣,然后再變換域丟棄小系數(shù),完成壓縮;

而壓縮感知不同,它的思想其實(shí)從圖像壓縮中借鑒了很多:既然全采樣了還要再丟棄,我們?yōu)槭裁床荒苤苯由俨蓸右恍c(diǎn)?因此,壓縮感知直接進(jìn)行了亞采樣,然后再用算法消除亞采樣導(dǎo)致的偽影。可以說,壓縮感知直接在采樣時(shí)就完成了壓縮。

---------------------------------------

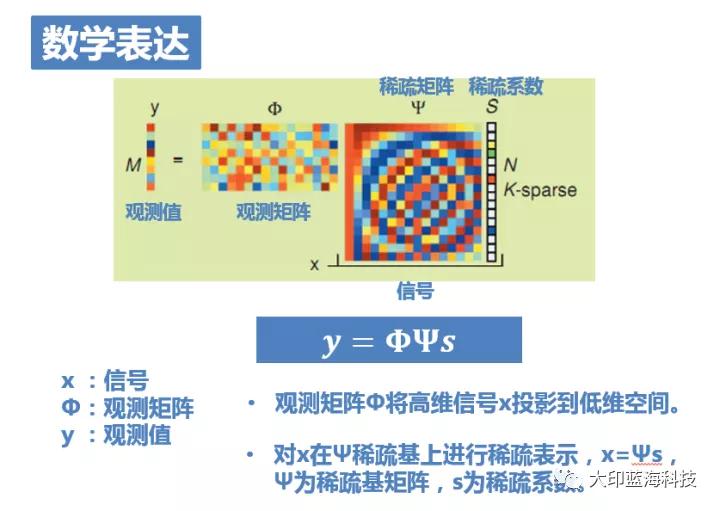

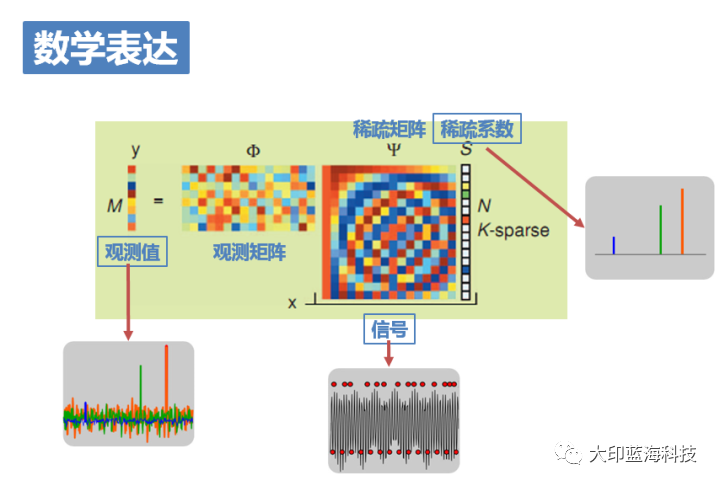

14. 接下來,在將第二個(gè)前提條件之前,還是需要引入必要的數(shù)學(xué)表達(dá)的。上圖是一個(gè)大家在壓縮感知相關(guān)的書籍文獻(xiàn)中會經(jīng)常看到的一張示意圖。很多文章試圖用這張圖給大家講清楚什么是壓縮感知,結(jié)果導(dǎo)致大家看得一頭霧水,混淆在各種“矩陣”當(dāng)中。。不過相信有了我之前的講解,現(xiàn)在這張圖會好理解很多。這張圖也就是把亞采樣的過程用矩陣的方式表達(dá)出來而已:

如圖,x是為長度N的一維信號,也就是原信號,稀疏度為k。此刻它是未知的。

Φ為觀測矩陣,對應(yīng)著亞采樣這一過程。它將高維信號x投影到低維空間,是已知的。

y=Φx為長度M的一維測量值,也就是亞采樣后的結(jié)果。顯然它也是已知的。

因此,壓縮感知問題就是在已知測量值y和測量矩陣Φ的基礎(chǔ)上,求解欠定方程組y=Φx得到原信號x。

然而,一般的自然信號x本身并不是稀疏的,需要在某種稀疏基上進(jìn)行稀疏表示。令x=Ψs,Ψ為稀疏基矩陣,s為稀疏系數(shù)。

于是最終方程就變成了:y=ΦΨs。已知y、Φ、Ψ,求解s。

---------------------------------------

15. 對應(yīng)一開始的例子大家就能明白:x就是三個(gè)正弦信號疊加在一起的原信號;稀疏矩陣Ψ就是傅里葉變換,將信號變換到頻域S;而觀測矩陣Φ就對應(yīng)了我們采用的隨機(jī)亞采樣方式;y就是最終的采樣結(jié)果。

---------------------------------------

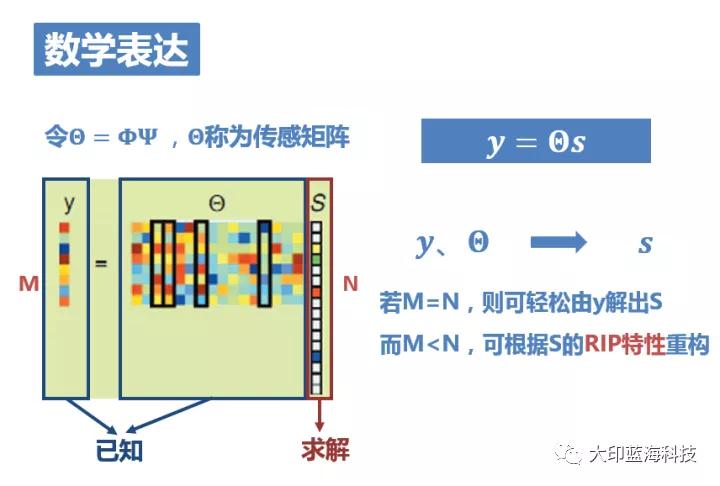

16. y=ΦΨs有點(diǎn)長,我們把ΦΨ合并成一個(gè)矩陣,稱之為傳感矩陣。即令Θ=ΦΨ

,則y=ΘS。

問題即為,已知y和Θ,求解S。

求解出S后,由x=Ψs即可得到恢復(fù)出的原信號x。

然而在正常情況下,方程的個(gè)數(shù)遠(yuǎn)小于未知數(shù)的個(gè)數(shù),方程是沒有確定解的,無法重構(gòu)信號。但是,由于信號是K稀疏,如果上式中的Φ滿足有限等距性質(zhì)(RIP),則K個(gè)系數(shù)就能夠從M個(gè)測量值準(zhǔn)確重構(gòu)(得到一個(gè)最優(yōu)解)。

---------------------------------------

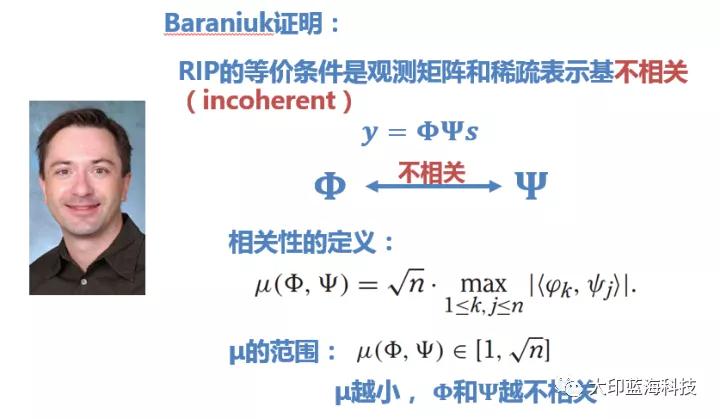

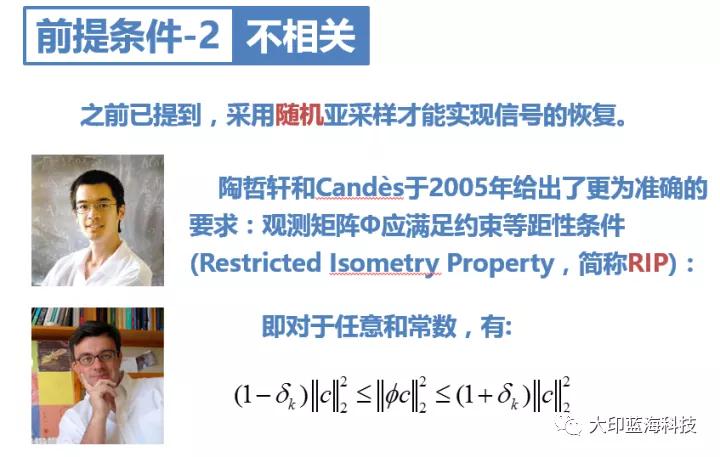

17.接下來的數(shù)學(xué)內(nèi)容可以簡短略過:陶大神和Candès大神證明了RIP才是觀測矩陣要滿足的準(zhǔn)確要求。但是,要確認(rèn)一個(gè)矩陣是否滿足RIP非常復(fù)雜。于是Baraniuk證明:RIP的等價(jià)條件是觀測矩陣和稀疏表示基不相關(guān)(incoherent)。

這就是壓縮感知的第二個(gè)前提條件。

---------------------------------------

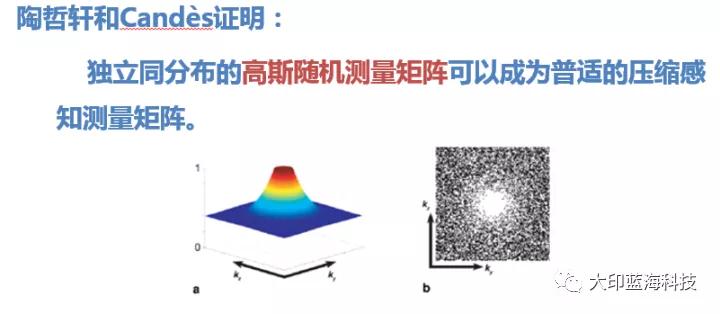

18. 那怎樣找到不相關(guān)的觀測矩陣呢?陶哲軒和Candès又證明: 獨(dú)立同分布的高斯隨機(jī)測量矩陣可以成為普適的壓縮感知測量矩陣。

于是滿足高斯分布的隨機(jī)測量矩陣就成了CS最常用的觀測矩陣。

對于二維信號,往往就采用如右上圖所示的采樣矩陣對圖像進(jìn)行亞采樣。

對于一維信號,采用前文提到的隨機(jī)不等間距的亞采樣即可。

------------------------------------------------------------------------------

到這里,我們可以這樣用一句話概括地描述什么是壓縮感知:

如果一個(gè)信號在某個(gè)變換域是稀疏的,那么就可以用一個(gè)與變換基不相關(guān)的觀測矩陣將變換所得高維信號投影到一個(gè)低維空間上,然后通過求解一個(gè)優(yōu)化問題就可以從這些少量的投影中以高概率重構(gòu)出原信號。

以上可以算作是壓縮感知的定義吧。但是如果要再簡潔一點(diǎn)呢?

在我看來,壓縮感知可以用這樣一句話來表述:

直接采集出一個(gè)JPEG

——之前圖像壓縮的方法是全采樣之后再壓縮,拋棄稀疏變換域中的一些小系數(shù);而CS直接減少了采樣點(diǎn),采集完后、經(jīng)過重建的圖像,就是一副在某變換域稀疏的壓縮圖像,比如JPEG。

那這么做有什么優(yōu)勢呢?

對于很多情形,比如照相機(jī)拍攝照片,這樣減少采樣點(diǎn)并沒有優(yōu)勢。因?yàn)樗邢袼氐牟杉谝凰查g就都完成了。

但是對于一些采集比較慢的情形,比如核磁共振成像,CS就可以發(fā)揮巨大優(yōu)勢。原本一副MRI圖像常常需要幾十秒,速度慢也是MRI的一大缺陷。而應(yīng)用CS技術(shù)后,只需要采集全采樣幾分之一的數(shù)據(jù),就可以重建出原圖。這樣就可以把成像速度提高好幾倍,同時(shí)對圖像質(zhì)量影響不大。

另一個(gè)應(yīng)用是Rice大學(xué)開發(fā)的單像素相機(jī),也就是說這種相機(jī)只需要一個(gè)像素,非常有趣。感興趣的朋友可以自己去調(diào)查。

三、壓縮感知的重建方法

如前文所述,CS的重建也就是求解欠定方程組y=ΘS的方法。這是一個(gè)零范數(shù)(l0)最小化問題,是一個(gè)NP完全問題(沒有快速解法的問題),因此往往轉(zhuǎn)換成一范數(shù)(l1)最小化的求解,或者用一些近似估計(jì)的算法。這部分的具體內(nèi)容在這里就不再詳述了。

------------------------------------------------------------------------------

以上就是壓縮感知的簡單講述。各方面都只是淺嘗輒止,更多內(nèi)容需還要大家自己研究。

其實(shí)寫這篇文章之前我已經(jīng)做好了受冷落的準(zhǔn)備,畢竟不像小波變換,壓縮感知的受眾面比較小,理解難度又比較大,大家閱讀時(shí)還請耐心一點(diǎn)。如果看后能對壓縮感知的主要思想有了一定的認(rèn)識,也就不枉我費(fèi)勁力氣畫了這么多圖、碼了這么多字。

*******************************************

把AFE集成到MCU,很難做到低offset,低溫漂吧?

這款在前級差分輸入的儀放(IA)后級跟上了取樣保持放大(SHA)與Delta-sigma ADC構(gòu)成的 IA+CS的AFE block

這是個(gè)很好的工程師常常提到的通用問題 MCU內(nèi)部是digital noisy 電源臟地環(huán)境,AFE是對noise敏度的. AFE內(nèi)部的high gain PGA對Vos是敏感的

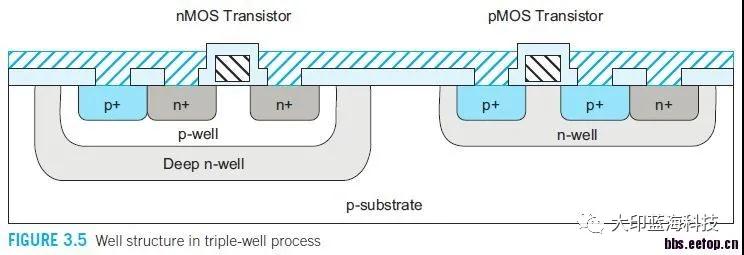

因此,AFE+MCU采用合封的方式是目前比較簡單粗暴的方式,但可能并不是die size最小成本甚至是最優(yōu)的。single die工藝就得找tri-well的 DNW隔離MCU ground 的noise進(jìn)analog部分了.

是的,NTN或DeepNwell都可以isolation。而我們常用的去除offset的方式便無可厚非地轉(zhuǎn)至chopper way.

關(guān)于Tri-well三阱,延伸拓展:

The twin well process is the process that contain 2 wells N and P. The tripple well process that contain another well implemented in the wells. like u have N well , implement a P well in it . It is usually used for RF circuits to achieve good isolation. For the tripple well process, Deep N-well was the third, usually. It can isolate p-well from P-substrate, so the p-well would not be tied to ground, it can be any potential. this is very useful for some circuits. For example, in the flash circuit, the tripple well process is must, because some circuits operate in the negative potential.

***** ********* ************** *****

In general MOS devices have 4 terminals D G S B.

B terminal [Bulk/Substrate] has an important role in MOS functionality. Fromthe back-side of a MOS the substrate potential can affect the channelcharacteristics - it resembles very similar functionality of a Gate terminal ofa FET [not a MOSFET but, a Field Effect Transistor], it is called back-gate.You want finer control of the back-gate - go get a triple-well MOS.

We call them isolated-MOS too - the reason being - electrically isolating thebulk node from global substrates.

Although it is not mandatory to keep Source & Substrate connection of a MOSbe shorted together, there are design requirements, where the S,B needs to belocally shorted - please note, I did not mention yet - S,B shorted to VDD or GND.Keep it at whatever different potential from global VDD/VSS you need atriple-well process.

Triple well further reduces signal and noise coupling to and from substrate[OK, same as noise isolation].

Triple well might help addressing different potential requirements at IO ESDregions.

Well, somewhere I might have read something about virtual power switching[power-gating] using back-gate [not sure].

All such things are possible by using triple well structures.

-http://www.edaboard.com/thread137886.html

*********************************

我們再聊聊Low Power LP低功耗設(shè)計(jì)

Deepnwell相當(dāng)于組成兩個(gè)背靠背的二極管,所以可以隔離p襯底耦合過來的噪聲, 更加強(qiáng)的噪聲隔離工藝是SOI絕緣體上硅工藝

RF應(yīng)用上的ground noise isolation也常用到DNW

降噪/低功耗設(shè)計(jì)是fabless design的根基

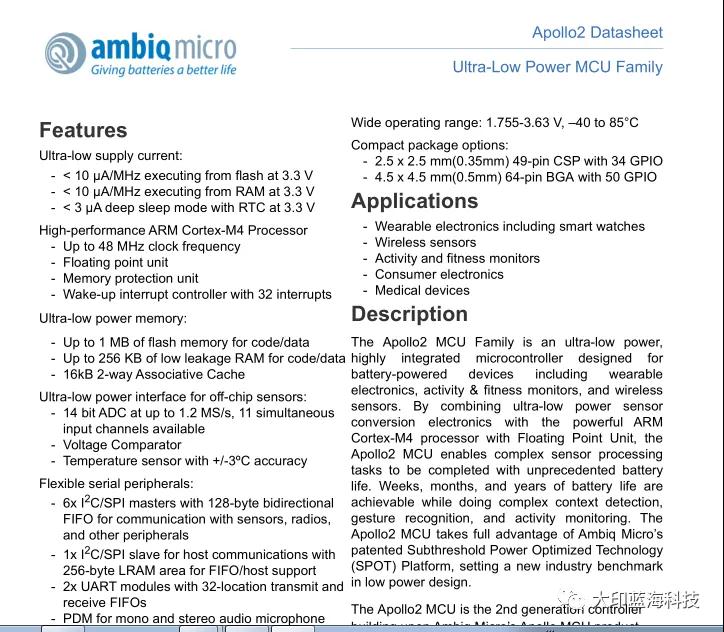

我這里借用了業(yè)內(nèi)知名的LP MCU 供應(yīng)商ambiq micro公司 2017年release的datasheet.

核心詞便是亞閥值:工作在subthreshold region

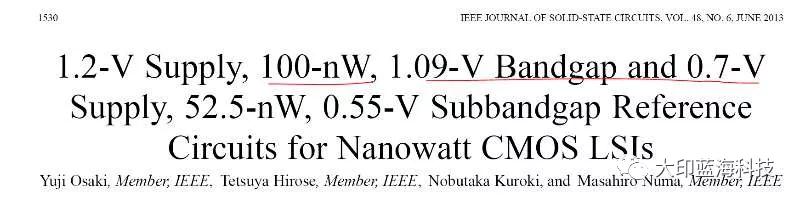

另一個(gè)核心詞便是低功耗帶隙基準(zhǔn) Bandgap Voltage Reference(BGR)

重新回到正題:

我們在討論,工作在subthreshold region BGR是否可以量產(chǎn)?原因是由于這種BGR的功耗可以做的非常低,MCU在deepsleep mode下通常需要低功耗的BGR.

普遍的一個(gè)觀點(diǎn)是可以量產(chǎn),但一致性比較差. 除非采用chopper否則offset會比較大甚至離譜到失控. 接下來我們可能會面臨著chopper與LPF設(shè)計(jì)時(shí)的size及trade off.

這里的chopper僅僅是消除offset,不針對相對敏度的高斯 1/f噪聲,所以可以直接用MCU中的IWDG noisy的時(shí)鐘(我們的工程師太可愛了),幾乎不用功耗;LPF的面積的確需要考慮

如上上圖IEEE Member提示的低功耗要到100nW,需要做Start-Up calibration,看起來具有挑戰(zhàn). 比如前些年Richtek被MTK并購整合forground calibration在PMIC里面, 每開機(jī)或ULP進(jìn)Normal mode前要校正(俗稱K)一次

ULP進(jìn)normal mode意思就是做兩套LDO, 因?yàn)橐狵過。ULP--> Normal 一次 Normal==> ULP 一次

在deepsleep模式下有BG+LDO+Clock在工作,關(guān)于Start-Up calibration, calibrate 產(chǎn)生VPTAT的單元, 通過調(diào)節(jié)電流和MOSs的寬長比?其實(shí)用準(zhǔn)的去K會變的, 做FSM用SAR ADC去做quantize量化, 然后feedback反饋調(diào)校正的code。

********************************

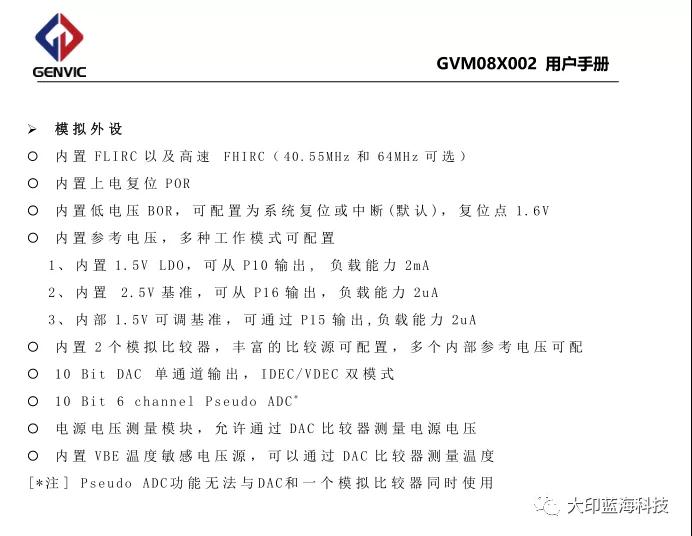

最后還剩點(diǎn)篇幅聊聊MCU的內(nèi)部Vref

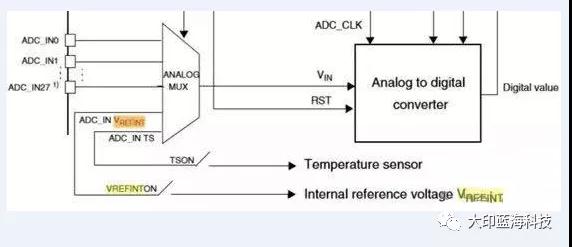

在使用MCU開發(fā)過程中,有人問如果電源電壓是變動的,詢問有無辦法用比較簡潔的辦法對電源電壓進(jìn)行監(jiān)測,或者說電源電壓波動情況下能否檢測出其它待測的AD輸入電壓。

這里跟大家分享交流一個(gè)方法。就是在沒有其它外來參考電壓,用芯片電源電壓VDD作為ADC的參考電壓,同時(shí)該電源電壓又在一定范圍內(nèi)變動的情況下【這個(gè)范圍就是在保證芯片正常工作的范圍】,利用MCU芯片內(nèi)部自帶基準(zhǔn)電壓對電源電壓進(jìn)行監(jiān)測。

在我印象中幾乎每顆MCU芯片內(nèi)部都有個(gè)相對穩(wěn)定且不受電源電壓一定范圍內(nèi)波動影響的基準(zhǔn)電壓。這里以普通8BIT MCU芯片為例來介紹。

51系列芯片內(nèi)部有個(gè)參考輸出電壓,技術(shù)手冊里命名為VREFINT。

健天電子GVM08X002 8位MCU內(nèi)置2.5V基準(zhǔn), 1.5V可調(diào)基準(zhǔn)輸出,輸出負(fù)載能力為2uA

這里提前厘清下:該內(nèi)部參考電壓VREFINT并非ADC的參考電壓,ADC的參考電壓依然是VDD。即使VDD有所波動,這個(gè)VREFINT電壓恒定不變,對于ADC電路而言,它只是個(gè)測試點(diǎn)。這里經(jīng)常有人犯迷糊,把VREFINT內(nèi)部基準(zhǔn)參考電壓跟ADC模塊的參考電壓混為一談。

在某一固定的ADC參考電壓情況下,所有被測電壓點(diǎn)的AD轉(zhuǎn)換值與該點(diǎn)電壓值保持同一比例關(guān)系,換句話說,對于ADC參考電壓固定情況下,各點(diǎn)的電壓與ADC值與成線性關(guān)系。

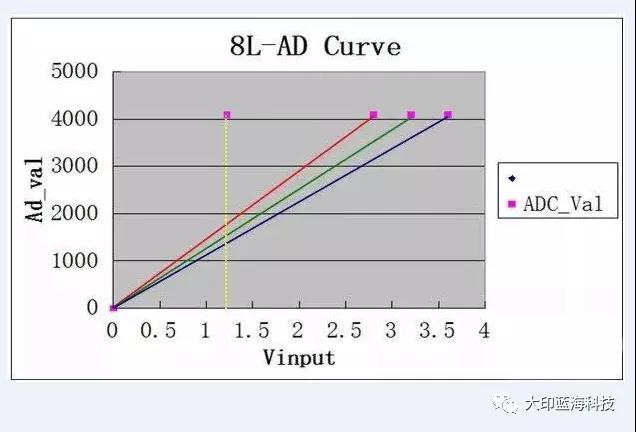

下面圖形是8位MCU芯片分別在3個(gè)不同參考電壓下的AD轉(zhuǎn)換曲線示意圖,這里參考電壓接不同的VDD。下面三根斜線分別是VDD為2.8V、3.2V、3.6V時(shí)的AD轉(zhuǎn)換曲線示意圖。那根[敏感詞]垂直虛線是表示內(nèi)部VREFINT電壓(1.22V)所在的位置。

不難理解,對于不同的參考電壓,同一待測電壓【VREFINT】1.22V所測得的AD轉(zhuǎn)換值是不一樣的,從上面圖也可以直觀的看出。這里AD的參考電壓就是VDD,顯然VDD越大,1.22V VREFINT電壓對應(yīng)的AD轉(zhuǎn)換值越小。

對于某一個(gè)參考電壓來說,如果能測得1.22V所對應(yīng)的AD轉(zhuǎn)換值,假設(shè)記為Val_AD1.2 那參考電壓VDD對應(yīng)的AD轉(zhuǎn)換值自然是此時(shí)該AD的滿量程值,記為 Val_Full,【如果精度是10位,就是1024,如果是12位,那就是4096】。

不管VDD怎么變動,某時(shí)刻的VDD對應(yīng)的滿量程值Val_Full跟內(nèi)部基準(zhǔn)電壓【VREFINT】1.22V的AD轉(zhuǎn)換值Val_AD1.2 的線性比例關(guān)系總是存在的。即有:

VDD:Val_Full = 1.22 : Val_AD1.2 【Val_AD1.2 為實(shí)時(shí)測得值】

那么VDD = (1.22 / Val_AD1.2) * Val_Full

這樣你就可以達(dá)到監(jiān)測芯片供電VDD的電壓之目的了。當(dāng)然你也可以利用上述原理和類似條件做別的應(yīng)用,比如說電源電壓一定范圍內(nèi)波動情況下還是可以檢測出其它待測點(diǎn)的電壓。

MCU內(nèi)部基準(zhǔn)可以用來做比較用,因?yàn)锳DC/DAC里面都會有比較器,用來比較輸入電壓和基準(zhǔn)電壓,得出比較結(jié)果,再轉(zhuǎn)化成相應(yīng)的數(shù)值. 有些應(yīng)用場合MCU內(nèi)部的ADC資源不夠用時(shí),也可以通過Vref配合DAC內(nèi)帶比較對外部輸入電壓進(jìn)行監(jiān)測。

免責(zé)聲明:本文轉(zhuǎn)載自“大印藍(lán)海科技”,本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號