引言

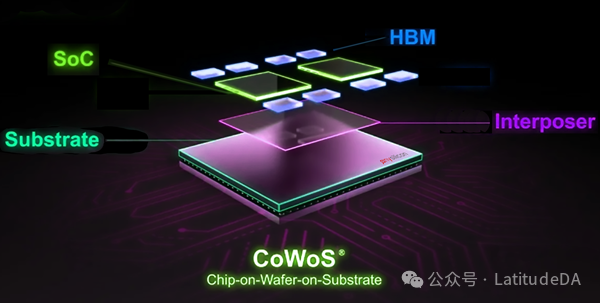

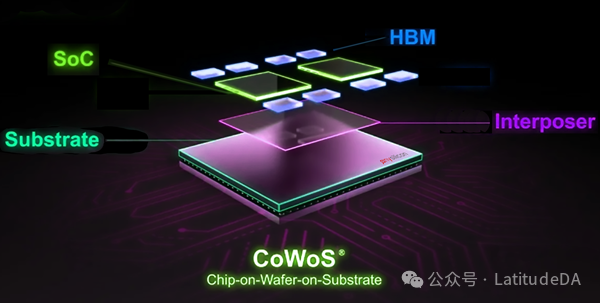

為了滿足高性能計算(HPC)和人工智能(AI)的計算需求,人們需要一種可擴展的封裝。片上基板(CoWoS)是一種先進的封裝技術,具有封裝尺寸更大、I/O 連接更多的優勢。它允許 2.5D 和 3D 組件堆疊,實現同質和異質集成。以前的系統面臨內存限制,而當代數據中心則采用高帶寬內存(HBM)來提高內存容量和帶寬。CoWoS 技術可在同一集成電路平臺上實現邏輯 SoC 和 HBM 的異質集成。

圖片來源: 臺積電

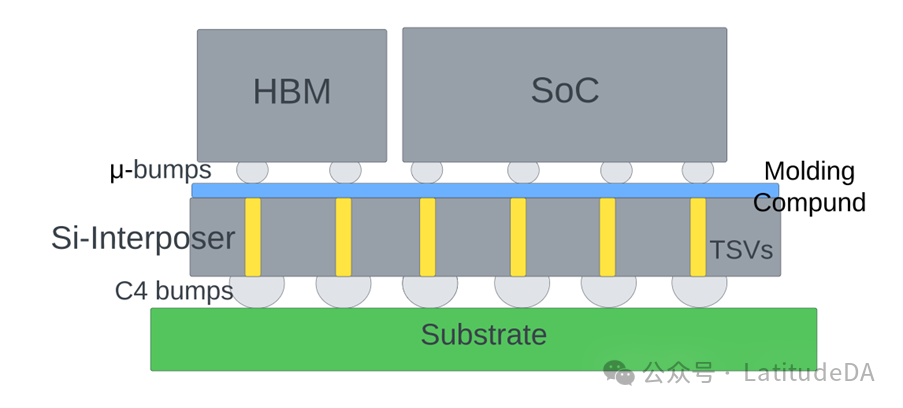

CoWoS 架構包括 2.5D 水平堆疊和 3D 垂直堆疊配置,徹底改變了芯片封裝的傳統模式。這種創新方法允許逐層堆疊各種處理器和內存模塊,創建相互連接的芯片,形成一個內聚系統。通過利用硅通孔(TSV)和微凸塊,與傳統的二維封裝方法相比,CoWoS 可縮短互連長度、降低功耗并增強信號完整性。

在實際應用中,CoWoS 技術可將 GPU 和人工智能加速器等高級處理單元與高帶寬內存(HBM)模塊無縫集成。這種集成對于人工智能應用尤為重要,因為在人工智能應用中,大規模計算能力和快速數據訪問是最重要的。CoWoS 將處理元件和內存元件就近配置,[敏感詞]限度地減少了延遲,提高了吞吐量,從而為內存密集型任務帶來前所未有的性能提升。

圖片來源: 臺積電

CoWoS 架構包括 2.5D 水平堆疊和 3D 垂直堆疊配置,徹底改變了芯片封裝的傳統模式。這種創新方法允許逐層堆疊各種處理器和內存模塊,創建相互連接的芯片,形成一個內聚系統。通過利用硅通孔(TSV)和微凸塊,與傳統的二維封裝方法相比,CoWoS 可縮短互連長度、降低功耗并增強信號完整性。

在實際應用中,CoWoS 技術可將 GPU 和人工智能加速器等高級處理單元與高帶寬內存(HBM)模塊無縫集成。這種集成對于人工智能應用尤為重要,因為在人工智能應用中,大規模計算能力和快速數據訪問是最重要的。CoWoS 將處理元件和內存元件就近配置,[敏感詞]限度地減少了延遲,提高了吞吐量,從而為內存密集型任務帶來前所未有的性能提升。

-

擴展性和更高的集成度: 傳統上,按照摩爾定律擴展晶體管有助于滿足對更高性能的需求。但事實證明,這對于高性能計算(HPC)、人工智能甚至圖形處理器(GPU)等現代應用來說是不夠的。CoWoS 允許在同一基板上堆疊芯片,從而減少同質或異質邏輯 SoC 之間以及 HBM 之間的互連延遲。

-

增強熱管理: 硅內插件和有機內插件的使用大大增強了堆疊集成電路的熱管理能力。這直接提高了整個系統的可靠性和壽命,同時[敏感詞]限度地降低了熱節流風險。

-

改善電源完整性: 堆疊集成電路內的電源/接地網絡使用 RDL,同時使用深溝槽電容器 (DTC),使高速應用和內存密集型應用的電源完整性不受影響。

-

縮小尺寸,降低成本:CoWoS 技術有助于將多個邏輯 SoC 和 HBM 安裝在相同的集成電路和基板上。這與傳統封裝技術形成鮮明對比,在傳統封裝技術中,多個邏輯 SoC 需要安裝在一塊印刷電路板(PCB)上,并在封裝中進行必要的連接。這導致封裝尺寸增大,材料成本和制造費用增加。CoWoS 封裝整體更小,成本效益更高。

人工智能、云計算、大數據分析和移動計算等技術的蓬勃發展導致對計算能力的需求日益增長。

現代社會對計算能力的高需求促進了人工智能芯片的發展,推動了對 CoWoS 等先進封裝解決方案的需求。

TrendForce 的數據顯示,人工智能服務器出貨量大幅增長,2023 年達到近 120 萬臺,預計 2022 年至 2026 年的復合年增長率為 22%。

對人工智能芯片的需求,尤其是對采用更高規格 HBM 的 GPU 的需求,導致臺積電 CoWoS 封裝的產能緊張,英偉達是其主要客戶。

由于供應短缺,臺積電的 CoWoS 封裝能力一直是人工智能芯片產出的瓶頸,尤其是在中間件領域。

臺積電計劃將 CoWoS 產能提高一倍,并投資先進的封裝廠,以期在 2024 年底前緩解供需失衡問題。

包括聯電、日月光科技控股公司和力成科技在內的其他臺灣公司正在進入 CoWoS 高級封裝市場,擴大產能并提供替代解決方案。

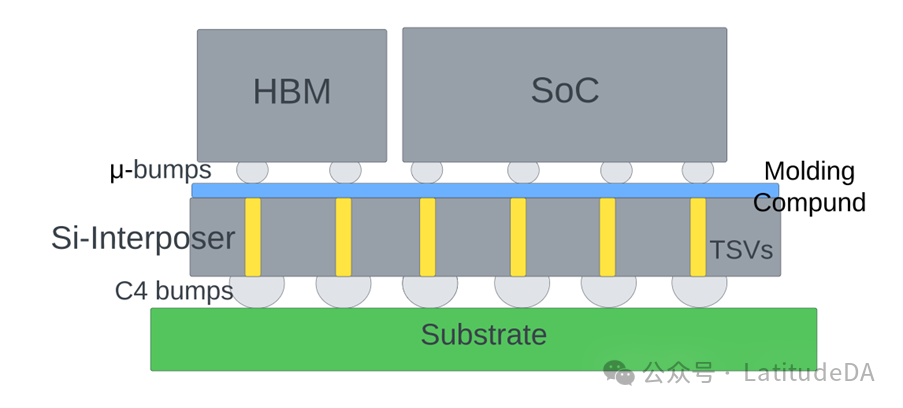

CoWoS-S:該技術使用單片硅內插件和硅通孔(TSV),以促進芯片和基板之間高速電信號的直接傳輸。不過,單片硅內插層存在良率問題。

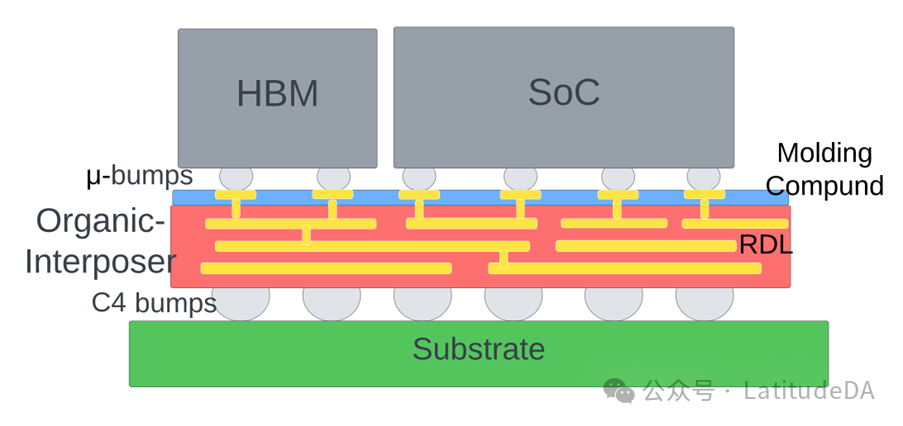

圖 1:CoWoS-S 封裝

CoWoS-R:這項技術用有機插層取代了 CoWoS-S 的硅插層。有機插層具有細間距 RDL,可在 HBM 和芯片甚至芯片和基板之間提供高速連接。與 CoWoS-S 相比,CoWoS-R 具有更高的可靠性和成品率,因為有機中間膜本身具有柔性,可作為應力緩沖器,減輕因基板和中間膜之間的熱膨脹系數不匹配而產生的可靠性問題。

圖 1:CoWoS-S 封裝

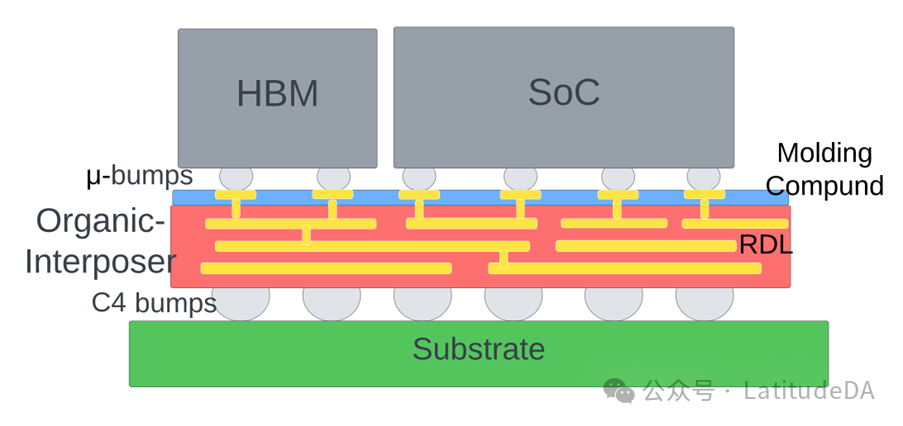

CoWoS-R:這項技術用有機插層取代了 CoWoS-S 的硅插層。有機插層具有細間距 RDL,可在 HBM 和芯片甚至芯片和基板之間提供高速連接。與 CoWoS-S 相比,CoWoS-R 具有更高的可靠性和成品率,因為有機中間膜本身具有柔性,可作為應力緩沖器,減輕因基板和中間膜之間的熱膨脹系數不匹配而產生的可靠性問題。

圖 2:CoWoS-R 封裝

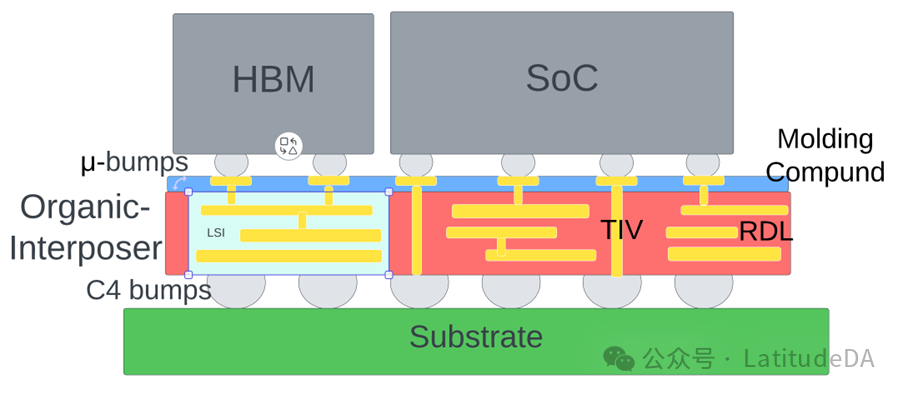

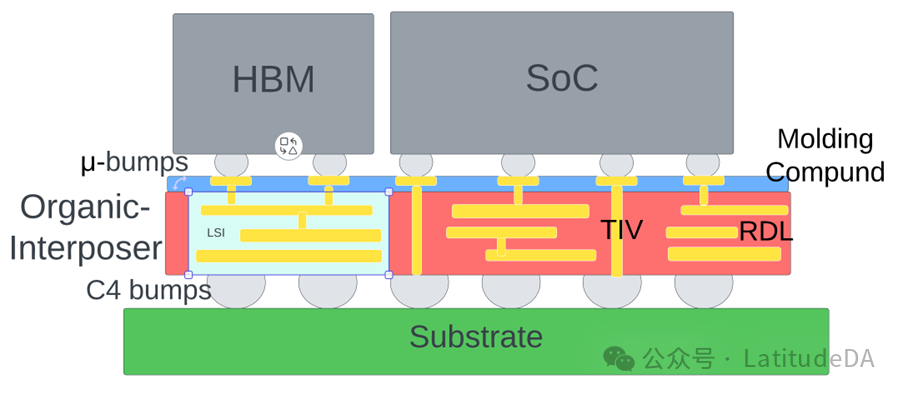

CoWoS-L 封裝:這種封裝使用本地硅互連(LSI)和 RDL 內插件,共同構成重組內插件(RI)。除了 RDL 內插件外,它還保留了 CoWoS-S 的誘人特點,即硅通孔 (TSV)。這也緩解了 CoWoS-S 中由于使用大型硅內插件而產生的良品率問題。在某些實施方案中,它還可以使用絕緣體通孔 (TIV) 代替 TSV,以[敏感詞]限度地降低[敏感詞]損耗。

圖 2:CoWoS-R 封裝

CoWoS-L 封裝:這種封裝使用本地硅互連(LSI)和 RDL 內插件,共同構成重組內插件(RI)。除了 RDL 內插件外,它還保留了 CoWoS-S 的誘人特點,即硅通孔 (TSV)。這也緩解了 CoWoS-S 中由于使用大型硅內插件而產生的良品率問題。在某些實施方案中,它還可以使用絕緣體通孔 (TIV) 代替 TSV,以[敏感詞]限度地降低[敏感詞]損耗。

圖 3:CoWoS-L 封裝

本節將討論 CoWoS-L 封裝的組成和制造步驟:

圖 3:CoWoS-L 封裝

本節將討論 CoWoS-L 封裝的組成和制造步驟:

1.CoWoS-L 是一種芯片末端組裝,因為首先要制造中間膜,然后在上面堆疊晶圓芯片。中間膜是 CoWoS 技術的關鍵原材料之一,因為多個晶圓芯片(如 SoC、HBM 等)都安裝在中間膜上,中間膜實現了芯片之間的有效連接和通信。中間膜制作完成后,下一步就是在晶圓裸片上制作直通絕緣通孔(TIV)。

2.然后在晶圓上安裝已知良好芯片(KGD)。晶粒和 TIV 之間的間隙用模塑化合物填充,然后使用 CMP 工藝獲得平面。

3.下一步是制作兩個 RDL 層

除此之外,CoWoS-L 技術還使用了深溝電容器 (DTC),可提供高電容密度,從而提高系統的電氣性能。這些電容器可充當電荷庫,滿足運行高速計算應用時的瞬時電流需求。

CoWoS 是一種 2.5D/3D 集成技術,與其前代產品相比,制造復雜度較高。制造復雜性直接導致采用這種封裝技術的芯片成本增加。這被認為是近來高性能計算和人工智能芯片成本增加的一個重要原因。CoWoS 的測試成本也增加了總成本。

5D 和 3D 集成電路需要像其他集成電路一樣進行測試,以確保它們不存在任何制造缺陷。然而,測試 2.5D 或 3D 集成電路的難度要大得多,因為在將每個晶圓裸片安裝到插接器上之前,都需要對其進行單獨測試,安裝后還需要再次測試。除此之外,還需要對硅通孔(TSV)進行測試。最后,大型硅內插件特別容易出現制造缺陷,并可能導致成品率下降。

CoWoS 封裝存在熱問題,這是因為中間膜與基底之間的熱膨脹系數 (CTE) 不同。使用有機中間膜可在一定程度上限制熱問題。使用底層填充材料可以緩沖硅芯片和基底之間的熱失配,從而大大延長焊點的使用壽命。

同樣,在正面,再分布層(RDL)的完整性,尤其是兩個硅芯片下面的再分布層,很容易受到應力的影響。使用 μ-bump 底部填充材料可在硅芯片和 RDL 之間起到應力緩沖作用。

CoWoS 封裝面臨信號和電源完整性方面的電氣挑戰。

(1)信號完整性:

邏輯晶片-芯片-基板互連: 隨著數據速率的提高,TSV 的寄生電容和電感會導致互連信號傳輸性能下降。為解決這一問題,我們努力優化 TSV,以盡量減少電容和電感。

邏輯晶圓-晶圓到 HBM:SoC 和 HBM 之間互聯的眼性能瓶頸在于互聯的寄生電阻和電容。

CoWoS 封裝通常用于具有較高數據切換率和較低工作電壓的高性能應用。因此,這些封裝容易受到電源完整性挑戰的影響。

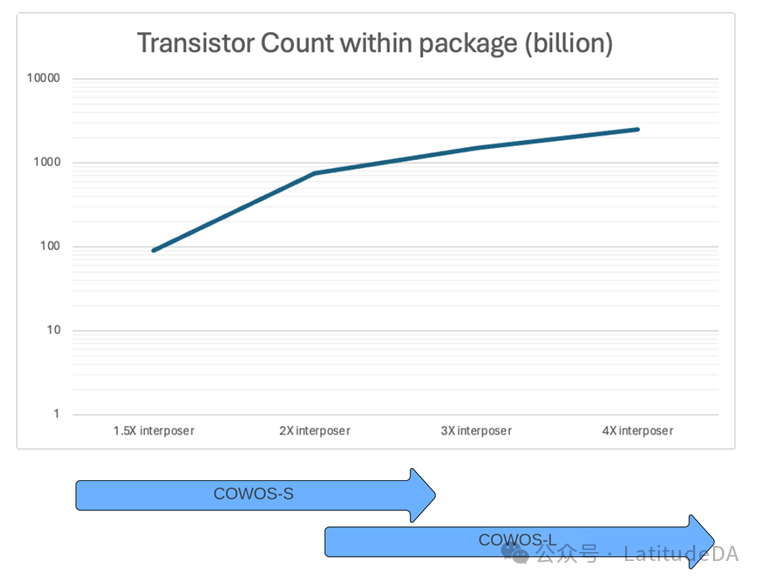

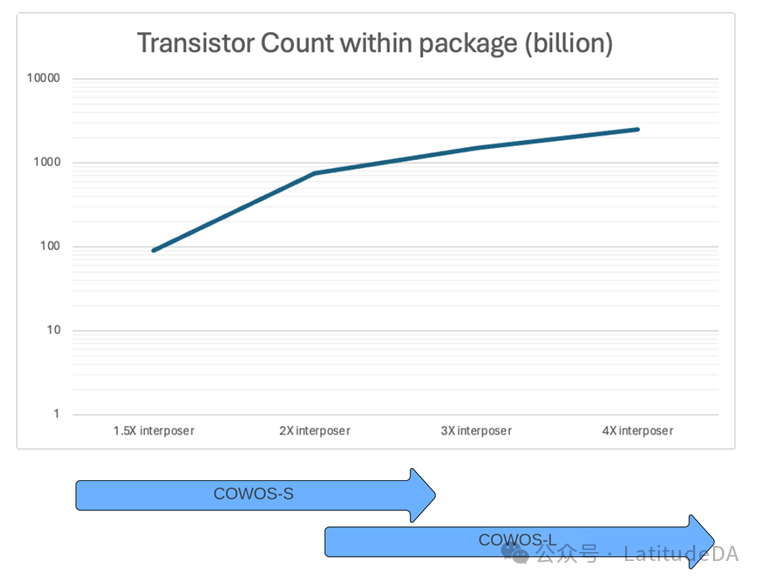

與系統級芯片 (SiP) 等老式封裝技術相比,CoWoS 技術可在封裝中支持更多晶體管。所有需要大量并行計算、處理大矢量數據和需要高內存帶寬的應用都最適合使用這種技術。

圖 4:隨著 CoWoS 的發展晶體管數量增加

圖 4:隨著 CoWoS 的發展晶體管數量增加

-

高性能計算 (HPC)。

-

人工智能 (AI) 和機器學習 (ML)。

-

網絡和數據中心

-

圖形處理器 (GPU) 和游戲。

許多公司都因 CoWoS 軟件包的成功而蓬勃發展。例如:

1.英偉達公司(NVIDIA)的人工智能芯片依賴于 CoWoS 軟件包。

2.AMD 也在探索將 CoWoS 封裝用于其人工智能芯片。

3.聯發科與臺積電合作,將 CoWoS 用于其網絡 ASIC。

4.博通公司(Broadcom)將 CoWoS-L 用于其滿足深度學習和網絡應用的 ASIC。

5.Global Unichip Corp. (GUC) 也與臺積電合作,將 CoWoS 用于其人工智能、高性能計算和網絡應用芯片。

CoWoS 技術提供了更高的集成度,使集成電路能夠擴展以滿足不斷增長的計算能力需求。該技術正在不斷發展,以確保更高的良率、穩健的電源和熱完整性,并進一步增加插層面積,使更多晶圓能夠共享同一基板。未來幾年,CoWoS 將繼續推動半導體行業的發展。

[1]https://anysilicon.com/cowos-package/

[2]“Test Challenges in Designing Complex 3D Chips: What in on the Horizon for EDA Industry”, by Sandeep K. Goyal.

[3]“Wafer Level System Integration of the Fifth Generation CoWoS?-S with High Performance Si Interposer at 2500 mm2”, by Huang et al.

[4]“CoWoS Architecture Evolution for Next Generation HPC on 2.5D System in Package”, by Hu et al.

- END -

免責聲明:本文采摘自網絡,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

圖片來源: 臺積電

圖片來源: 臺積電

圖 1:CoWoS-S 封裝

圖 1:CoWoS-S 封裝

圖 2:CoWoS-R 封裝

圖 2:CoWoS-R 封裝

圖 3:CoWoS-L 封裝

圖 3:CoWoS-L 封裝

圖 4:隨著 CoWoS 的發展晶體管數量增加

圖 4:隨著 CoWoS 的發展晶體管數量增加