服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2023-12-15作者來源:張國斌瀏覽:1519

“今年芯耀輝的員工很忙,一部分人在加班加點(diǎn)開發(fā)產(chǎn)品,一部分在支持客戶規(guī)模量產(chǎn)。”在今年的ICCAD2023的媒體專訪中,芯耀輝董事長曾克強(qiáng)表示,“經(jīng)過三年多的自主研發(fā),芯耀輝已開發(fā)出基于國產(chǎn)工藝全系列接口IP,包括PCIe、Serdes、DDR、D2D、USB、MIPI、HDMI、SATA,SD/eMMC等涵蓋[敏感詞]協(xié)議標(biāo)準(zhǔn)的全棧式完整IP解決方案,包括LPDDR5、DDR5和片間互聯(lián)的D2D IP。目前,我們正積極將這些產(chǎn)品引用到行業(yè)主流工藝中進(jìn)行測試,此外,要實(shí)現(xiàn)Chiplet技術(shù)的真正落地,高質(zhì)量的接口IP是不可或缺的。”

團(tuán)隊(duì)研發(fā)的DDR5/4 PHY在相關(guān)工藝上超越了全行業(yè)[敏感詞]速率;推出的LPDDR5/4 PHY極具PPA競爭力及優(yōu)異的易實(shí)現(xiàn)性及互操作性;完整的UCIe D2D解決方案包括PHY及控制器,可支持UCIe協(xié)議且兼容D2D和C2C場景。

“在芯耀輝之前,大家可以看到國內(nèi)的廠商基本上能夠?qū)崿F(xiàn)的做到的接口IP的標(biāo)準(zhǔn)一般都還是比較傳統(tǒng)的,像DRR3、PCIE3等,但是最領(lǐng)先的標(biāo)準(zhǔn)比如說DDI5、PCIE5沒有,這也是我們芯耀輝從成立之日起的時(shí)候要做的事情,我們就希望在這一塊真正能夠做前人沒做過的事,真正填補(bǔ)空白。”他強(qiáng)調(diào)。“接口IP也是當(dāng)下整個(gè)IP領(lǐng)域需求最旺,增速最快的應(yīng)用領(lǐng)域,也是除了處理器以外規(guī)模[敏感詞]的細(xì)分市場。”

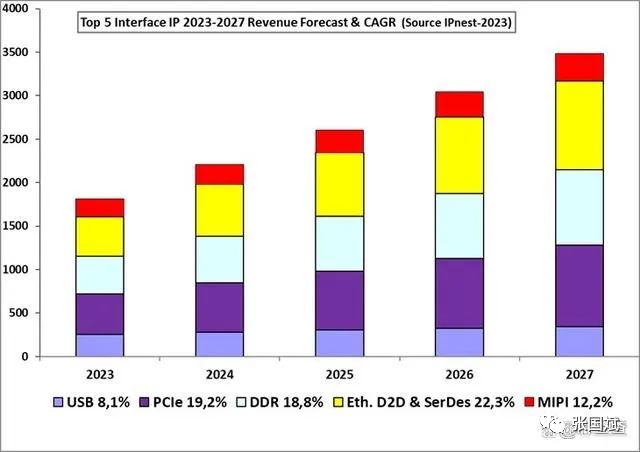

IPnest對(duì)接口IP未來5年進(jìn)行了預(yù)測(2023-2027)大部分增長預(yù)計(jì)來自三個(gè)類別:PCIe、內(nèi)存控制器(DDR)、以太網(wǎng)&D2D,5年復(fù)合年增長率分別為19.2%、18.8%和22.3%,這些協(xié)議都與數(shù)據(jù)應(yīng)用相關(guān)。2022年前5大接口協(xié)議的市場規(guī)模為14.4億美元,預(yù)測2027年將提升至35億美元,即復(fù)合年增長率18%。

曾克強(qiáng)表示,芯耀輝在IP領(lǐng)域擁有獨(dú)特的優(yōu)勢,主要體現(xiàn)在以下兩點(diǎn):

1、符合國際標(biāo)準(zhǔn)協(xié)議的定制化設(shè)計(jì):芯耀輝專注于制定符合國際標(biāo)準(zhǔn)協(xié)議的接口IP,不僅滿足這些標(biāo)準(zhǔn)協(xié)議的要求,還根據(jù)客戶的客戶的不同應(yīng)用場景和產(chǎn)品形態(tài),提供滿足這些標(biāo)準(zhǔn)協(xié)議的定制化需求。例如,對(duì)于消費(fèi)類產(chǎn)品,客戶可能更關(guān)注功耗和面積,即所謂的的PPA(功耗、性能、面積),而除了在PPA方面取得平衡外,客戶最看重的是一次量產(chǎn)成功,要求IP做到高可靠性和強(qiáng)兼容性。“這也是我們最看重的地方,甚至超過了PPA的考量”他強(qiáng)調(diào)。

2、專業(yè)團(tuán)隊(duì)進(jìn)行系統(tǒng)級(jí)驗(yàn)證:由于芯耀輝在IP領(lǐng)域有持續(xù)15-20年的積累,公司建立了幾十人的經(jīng)驗(yàn)豐富專業(yè)團(tuán)隊(duì),專門負(fù)責(zé)可靠性和兼容性測試,從系統(tǒng)級(jí)到芯片電路級(jí)進(jìn)行全方位的驗(yàn)證。

“例如,在可靠性方面,芯耀輝會(huì)針對(duì)IP進(jìn)行溫度、電壓以及制造工藝的拉偏測試,并且還會(huì)進(jìn)行ESD靜電防護(hù)能力測試以及長時(shí)間的高溫老化測試,確保IP在客戶芯片量產(chǎn)上沒有良率的問題。同時(shí)我們也會(huì)針對(duì)客戶實(shí)際應(yīng)用場景,以及積累多年的非標(biāo)準(zhǔn)場景,進(jìn)行[敏感詞]環(huán)境下(比如高通道損耗,長時(shí)間不間斷傳輸?shù)龋┑腎P性能測試,保障IP具備高度的可靠性。”他補(bǔ)充說,“而在兼容性方面,不同的接口IP都會(huì)和市場上主流的相關(guān)外設(shè)做互聯(lián)互通兼容測試。舉個(gè)例子,常用的接口DDR5,針對(duì)市場上最常用的應(yīng)用廠商的顆粒,比如說三星、海力士、美光和國內(nèi)成熟廠商等等,我們都會(huì)收集它主要的顆粒,針對(duì)不同的速率、不同的DIMM,我們都會(huì)去做測試,不僅是普通的讀寫,甚至?xí)磸?fù)的初始化,考驗(yàn)產(chǎn)品的訓(xùn)練過程和性能,確保接口IP能做到完備的測試,這應(yīng)該是國內(nèi)的廠商里[敏感詞]的,所以保證了我們交付給客戶的產(chǎn)品,除了在PPA上滿足客戶的需求,更在可靠性和兼容性上幫助客戶的產(chǎn)品一次量產(chǎn)成功,降低產(chǎn)品風(fēng)險(xiǎn),縮短產(chǎn)品上市時(shí)間。”

他表示經(jīng)過三年的研發(fā),芯耀輝已經(jīng)在國產(chǎn)先進(jìn)工藝已經(jīng)實(shí)現(xiàn)了所有接口IP主流的全套量產(chǎn)交付,尤其是針對(duì)高性能計(jì)算,最主要的應(yīng)用場景就是CPU、GPU、AI,他們其中主要的接口IP的需求主要是兩大類,一類是存儲(chǔ)器接口,一類是片間互聯(lián)。如DDR5、LPDDR5等芯耀輝都已經(jīng)完成自研,并且實(shí)現(xiàn)量產(chǎn)交付。

針對(duì)片間互聯(lián),芯耀輝的PCIE4、PCIE5都是行業(yè)目前[敏感詞]的,也完成量產(chǎn)交付,包括die to die的UCIe。

“Chiplet技術(shù)的核心在于將芯片的性能和工藝進(jìn)行解耦,將一個(gè)復(fù)雜的SoC大芯片根據(jù)其不同功能分成不同小芯片,這些小芯片可以采用不同的工藝來異構(gòu)集成。理想情況下,這種集成應(yīng)該在效率和連接性上類似于同一顆芯片,即像同一顆芯片的片間總線一樣高效互聯(lián)。然而,實(shí)際情況下,由于不同芯片的連接會(huì)帶來一定損耗,而且許多芯片需要大量連線,這帶來了一個(gè)現(xiàn)實(shí)中的問題。要實(shí)現(xiàn)Chiplet技術(shù),最本質(zhì)的挑戰(zhàn)是實(shí)現(xiàn)片間的高效互聯(lián),而真正的互聯(lián)問題是Chiplet技術(shù)落地中最為核心的方面。在這個(gè)過程中,對(duì)接口IP的需求顯得尤為關(guān)鍵”他分析說,“芯耀輝是[敏感詞]批加入U(xiǎn)CIe組織的國內(nèi)廠商,也是參與制定[敏感詞]中國原生Chiplet技術(shù)標(biāo)準(zhǔn)《小芯片接口總線技術(shù)要求》(T/CESA 1248-2023)的重點(diǎn)貢獻(xiàn)企業(yè),同時(shí)也是中國Chiplet《芯粒互聯(lián)接口標(biāo)準(zhǔn)(ACC1.0)》和《車規(guī)級(jí)芯粒互聯(lián)接口標(biāo)準(zhǔn)(ACC_RV1.0)》的起草和審閱單位;另外,我們還承接了國家科技部重點(diǎn)研發(fā)計(jì)劃“芯粒集成的統(tǒng)一網(wǎng)絡(luò)架構(gòu)和接口規(guī)范研究”項(xiàng)目,從產(chǎn)學(xué)研多方面推動(dòng)國內(nèi)Chiplet技術(shù)落地及生態(tài)鏈的發(fā)展。”

他指出,在開發(fā)Chiplet時(shí),封裝是一個(gè)關(guān)鍵要素。因此,在芯耀輝進(jìn)行接口IP設(shè)計(jì)時(shí),他們就考慮了與芯片接口IP設(shè)計(jì)和封裝設(shè)計(jì)之間的協(xié)同設(shè)計(jì)。芯耀輝已經(jīng)和國內(nèi)多家先進(jìn)封裝廠商聯(lián)合研發(fā),以在提供給客戶接口IP時(shí)就充分考慮后端封裝的實(shí)現(xiàn)性。

他表示,芯耀輝不僅支持國外廠商的先進(jìn)封裝,也支持國內(nèi)一些2.5D封裝,同時(shí)針對(duì)國內(nèi)產(chǎn)業(yè)鏈的現(xiàn)狀,也支持傳統(tǒng)標(biāo)準(zhǔn)封裝。“芯耀輝是國內(nèi)[敏感詞]家完成UCIe die to die的IP。今年年末,我們將完成[敏感詞]客戶量產(chǎn)交付”他強(qiáng)調(diào)。

展望未來,他表示芯耀輝看好高性能計(jì)算、人工智能和汽車領(lǐng)域。從2021年開始,芯耀輝已經(jīng)開始在相應(yīng)的接口IP領(lǐng)域進(jìn)行布局。截至2023年,芯耀輝已經(jīng)通過了與車規(guī)相應(yīng)的ACQ-100和ISO26262的國際測試認(rèn)證。因此,芯耀輝是國內(nèi)[敏感詞]能夠提供符合車規(guī)認(rèn)證的接口IP廠商,為未來汽車的市場做好充分的準(zhǔn)備。(完)

人劃線

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號(hào)