服務熱線

0755-83044319

發布時間:2022-03-09作者來源:薩科微瀏覽:3591

當今的電子設備市場需要將多種高速功能集成在一塊板上的小型化印刷電路板 (PCB)上,這導致設計人員將走線布置得非常靠近,以優化封裝和空間。這種接近可能會導致電磁場的意外耦合,這種現象稱為串擾(見圖 1) - 英文里的Crosstalk。

圖 1:PCB 上具有潛在串擾問題的相鄰走線的圖示。

盡管高密度的封裝是不可避免的,但還是不應違反某些與PCB上的布線相關的 PCB設計規則,以避免潛在的串擾和電磁干擾/兼容性 (EMI/EMC) 問題。

(在以下部分中,短語“關鍵網絡”指的是PCB上那些高速時鐘/數據線、重要的傳感線等,具體取決于PCB的應用。)

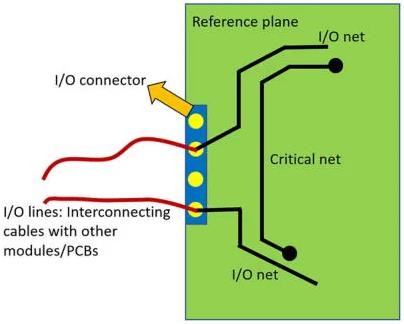

規則 1:I/O 網絡附近的關鍵網絡

重要的是要查看與I/O線相關的關鍵網絡的走線,因為噪聲很容易通過這些進出PCB的I/O 線耦合進電路板(見圖 2)或將噪聲帶到其它電路板。

圖 2:關鍵網絡和 I/O 網絡彼此靠近布線的場景示意圖。

通過 I/O 線進入電路板的任何噪聲都有可能耦合到承載重要數據/時鐘信號的關鍵網絡,這基本上是 PCB 的抗擾性問題(圖 3a)。以類似的方式,關鍵網絡攜帶的任何高速信號都可以耦合到 I/O 網絡,最終通過離開電路板的 I/O 線傳到外部世界并進入系統中的其它模塊。原則上,這將是PCB的輻射問題(圖 3b)。

圖 3a(左)和 3b:由關鍵網絡和 I/O 網絡的接近引起的潛在 EMI/EMC 問題

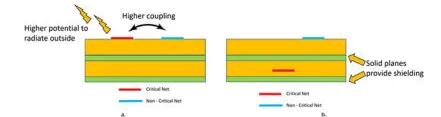

規則 2:暴露的關鍵跡線長度

在波長較短的高速 PCB (> 100MHz) 上,任何關鍵網絡(見圖 4a)的電氣長度都足以使其成為有效的輻射源,尤其是當暴露在頂層或底層時。 這種不需要的輻射可以耦合到任何相鄰的走線,甚至耦合到靠近走線的器件中的線纜中。 我們建議將關鍵網絡埋在PCB內層的實心平面之間,如圖 4b 所示。 這有助于封閉住來自走線的場并避免任何以串擾或EMI形式出現的意外耦合。 如果不得不將這些關鍵網絡暴露在外層,則暴露部分的長度應盡可能小。 這是因為暴露走線的長度越短,輻射的就越少,因為如果它們在電氣上很小,它們將是低效的天線。

圖 4a(左)和 b:在平面之間暴露或封閉關鍵網絡的圖示

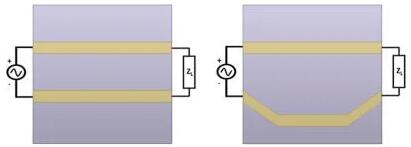

規則 3:臨界差分網絡匹配

理論上,差分對傳輸大小相等但極性相反的信號,因為差分對產生的EMI互相抵消或可以忽略不計。 但是,這僅在線對中的走線長度相等并且盡可能對稱地彼此靠近時才有效。 違反其中任何一項都會產生共模噪聲和 EMI 問題。 這是一個非常值得關注的問題,特別是對于承載高頻關鍵信號的差分網絡,因為 EMI 會增加所承載信號的頻率。 圖5顯示了在 IC 封裝和電路板上的出口點(連接器)之間關鍵差分對的正確/不正確方法的幾個走線示例。

圖 5:參考平面中存在分開時的返回電流路徑

臨界差分網絡匹配:模擬和與實際測試要求的關系

在圖 6a 和 6b 的 PCB 示例中,我們有一個簡單的案例,即差分對以兩種不同的方式在 PCB 上布線:分別是對稱和非對稱。 在這兩種情況下,在 SIwave 中,它們的一端由差分電壓源激勵,另一端由負載端接。

圖 6a(左)和 b:在 PCB 上布線的差分對示例

我們在這兩種情況下都運行近場分析。在差分對對稱布線的 PCB 中,近場電平低于它們不對稱布線的情況,如圖 7a 和 7b 所示。

圖 7a(左)和 b:具有對稱和非對稱差分對網絡的近場 @ 597.45 MHz

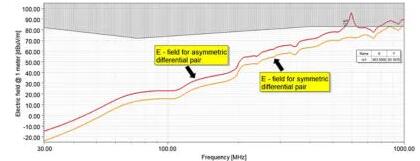

假設我們要根據 EMI/EMC 法規 AIS 004(在印度)或 UNECE R10(在歐洲)輻射發射要求來測試該 PCB。圖 8 顯示了在 30 MHz ? 1 GHz 頻率范圍內,距離該 PCB 1 米處的模擬遠場的比較分析。請注意,不對稱差分對的情況會使發射電平增加約 8 到 10 dB,也會導致不符合 563.50 MHz 及更高頻率的情況。

圖 8:1 米輻射比較

SIwave 在 PCB 級別上的仿真能夠及早識別此類 EMI 問題,這有助于在將 PCB 設計用于物理測試甚至更高級別的仿真之前對其進行優化。

免責聲明:本文轉載自“ 電子森林”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號