服務熱線

0755-83044319

發布時間:2024-08-13作者來源:薩科微瀏覽:1502

最近有熱心讀者希望了解:當半導體技術從FinFET轉向GAA(Gate-All-Around)時,會對蝕刻、清洗、CVD/PVD等制造工藝產生一系列影響。

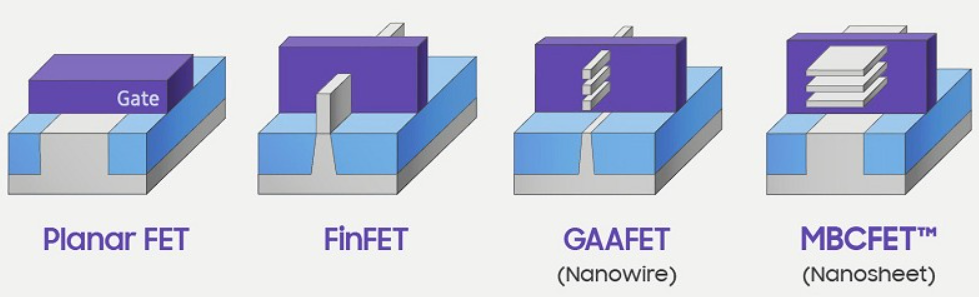

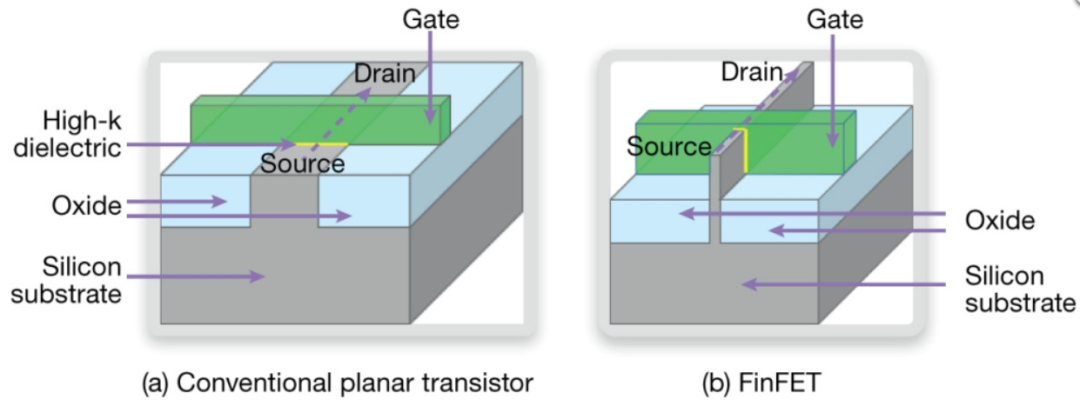

一、FinFET與GAA結構的差異

FinFET結構:FinFET是一種三維結構,柵極圍繞著從襯底突出出來的硅鰭狀結構。

GAA結構:GAA是一種更高級的三維結構,柵極完全包圍著納米線或納米片,從而提供更好的電氣控制。

圖:FinFET和GAAFET示意

二、對蝕刻工藝的影響

FinFET中的蝕刻:需要高各向異性蝕刻工藝來形成鰭狀結構。在形成鰭結構的過程中,需要高選擇性蝕刻來避免損壞周圍的材料。

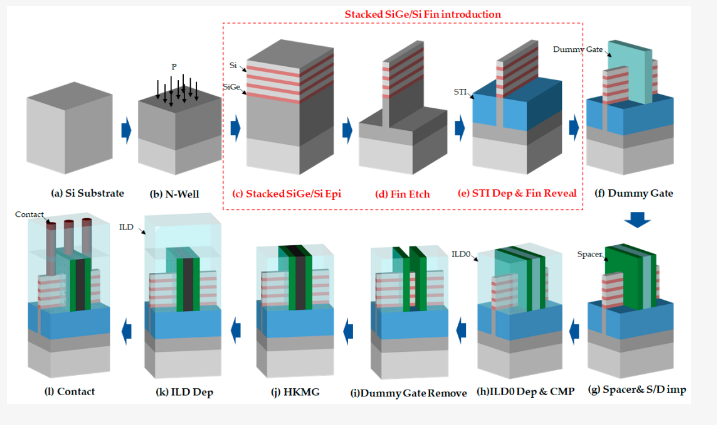

圖:SiGe/Si Channel FinFET device生產工藝

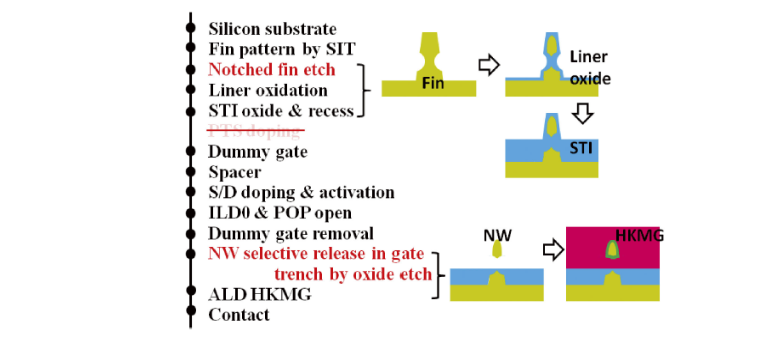

GAA中的蝕刻:由于GAA中納米線或納米片的精細尺寸,蝕刻工藝需要更高的精度。需要對多層材料進行選擇性蝕刻,以確保納米線或納米片的完整性。可能需要引入新型蝕刻氣體或等離子體,以實現對納米結構的高保真度蝕刻。

圖:GAA-SNWT的生產工藝

三、對清洗工藝的影響

FinFET中的清洗:主要針對鰭結構的清洗,重點在于去除光刻膠和蝕刻殘留物。

GAA中的清洗:由于GAA結構更加復雜,清洗工藝需要避免對納米線或納米片的損傷。需要引入更溫和、更有效的清洗溶劑和方法,以防止對細小結構的腐蝕和損傷。

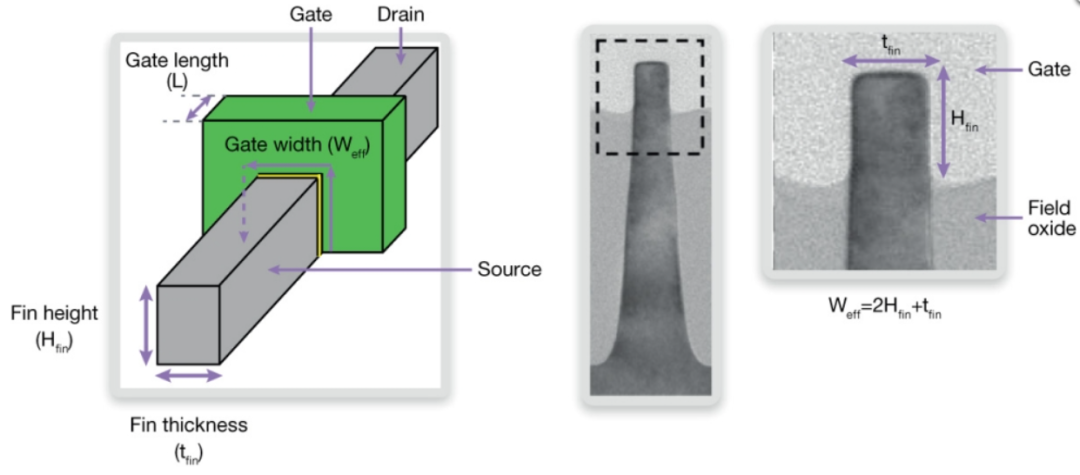

圖:傳統FET跟FinFET對比

四、對CVD/PVD工藝的影響

FinFET中的CVD/PVD:CVD(化學氣相沉積)和PVD(物理氣相沉積)主要用于鰭結構的柵極材料沉積和絕緣層沉積。要求良好的沉積均勻性和填充性。

GAA中的CVD/PVD:由于GAA結構需要完全包圍納米線或納米片,CVD/PVD工藝需要具備更高的沉積均勻性和精確控制能力。需要開發新的沉積材料和工藝,以適應納米線或納米片的包覆要求。可能需要使用ALD(原子層沉積)等更精細的沉積技術,以確保每一層材料的均勻性和厚度控制。

圖:FinFET器件的尺寸示意

五、其他相關工藝的影響

光刻:GAA結構對光刻技術提出了更高的要求,需要更高分辨率的光刻技術來定義精細結構。可能需要引入EUV(極紫外光刻)技術,以滿足更小尺寸的需求。

材料選擇:由于GAA結構中的納米線或納米片對材料性能的敏感性,需要選擇具有更高電氣性能和熱穩定性的材料。

封裝技術:GAA結構的復雜性對后續的封裝技術也提出了新的挑戰,需要確保納米結構在封裝過程中的完整性和功能性。

總結來說,從FinFET到GAA的轉變對半導體制造的各個方面都提出了更高的要求,特別是在蝕刻、清洗和CVD/PVD等關鍵工藝上,需要進行技術的改進和創新,以適應新結構的制造需求。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號