服務熱線

0755-83044319

發布時間:2024-09-19作者來源:薩科微瀏覽:2024

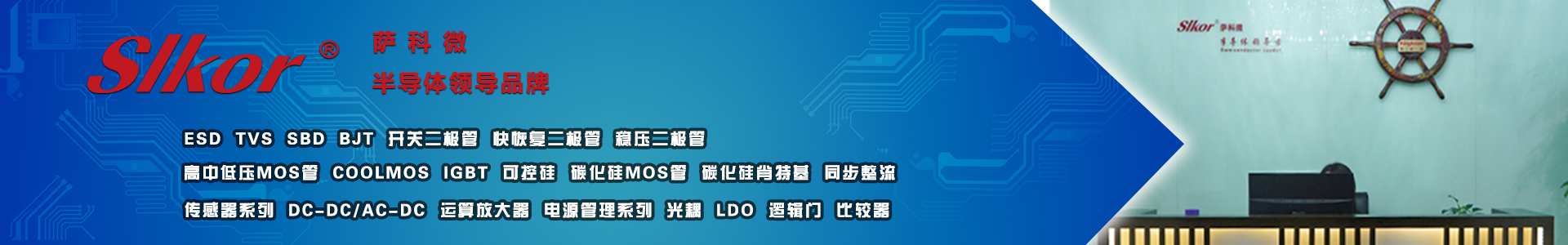

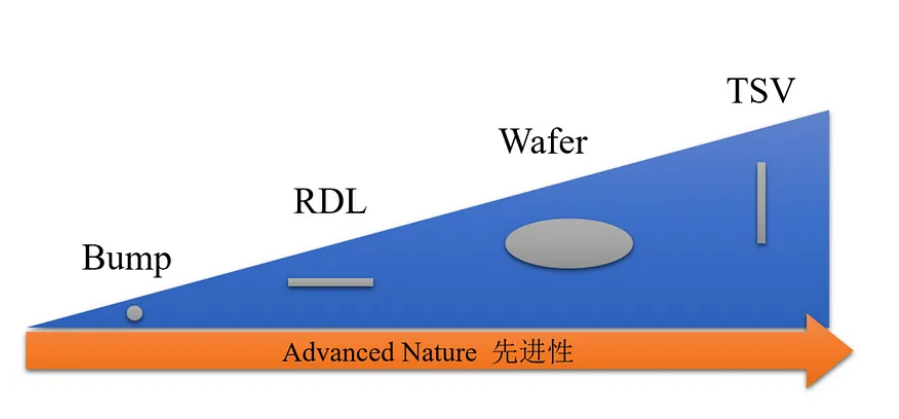

先進封裝的四大要素——TSV(硅通孔)、Bump(凸點)、RDL(重布線層)、Wafer(晶圓)——在現代半導體封裝中扮演了核心角色。它們在封裝工藝中各自承擔的功能,從不同維度推動了芯片小型化、集成度和性能的提升。

1. Wafer(晶圓):基礎材料和封裝載體

Wafer 是先進封裝的基礎,作為芯片制造的載體和平臺。它由高純度的硅材料制成,晶圓的質量和尺寸直接影響芯片的性能和良率。先進封裝中,Wafer不僅是芯片制造的核心,也是未來異質集成和多芯片封裝的基礎。

技術作用:晶圓是所有半導體電路加工的基礎,芯片的電路都是在晶圓上進行光刻、刻蝕和沉積等復雜工藝加工而成。

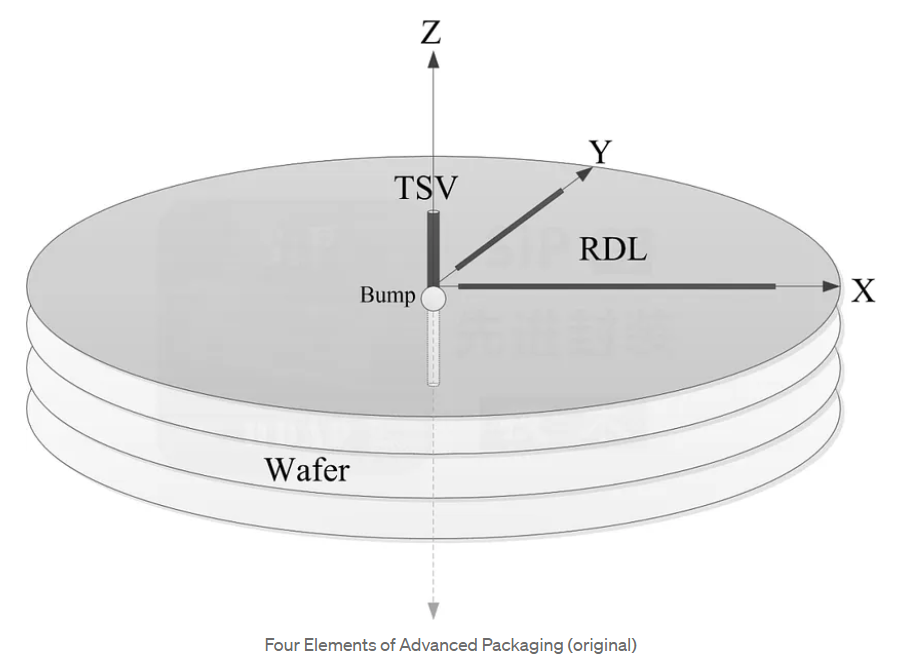

隨著晶圓尺寸的增大(如從200mm到300mm),可以在單個晶圓上制造更多芯片,從而提升生產效率,降低成本。

晶圓的純度和表面平整度對于芯片的性能至關重要,尤其是在先進制程(如3nm、2nm)下,對結構缺陷的控制要求極高。

為什么Wafer是四大要素之一:Wafer作為封裝和集成電路的核心材料,是所有后續封裝步驟的基礎載體。沒有高質量的晶圓,后續的TSV、Bump、RDL等技術也無法實現高效集成。

2. Bump(凸點):芯片與封裝基板的電氣和機械連接

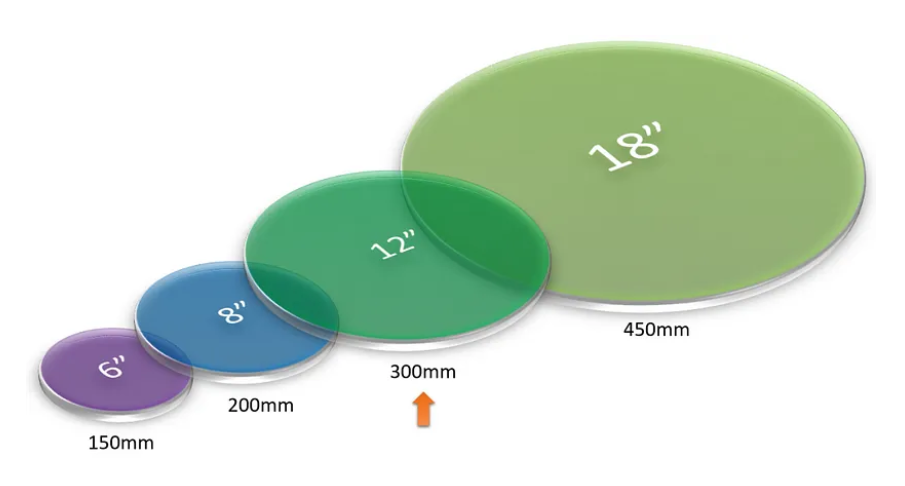

Bump 是實現芯片與封裝基板之間連接的重要元素,類似于橋梁連接兩者。通過Bump,電信號可以從芯片傳輸到封裝基板,完成芯片與外部系統的通訊。

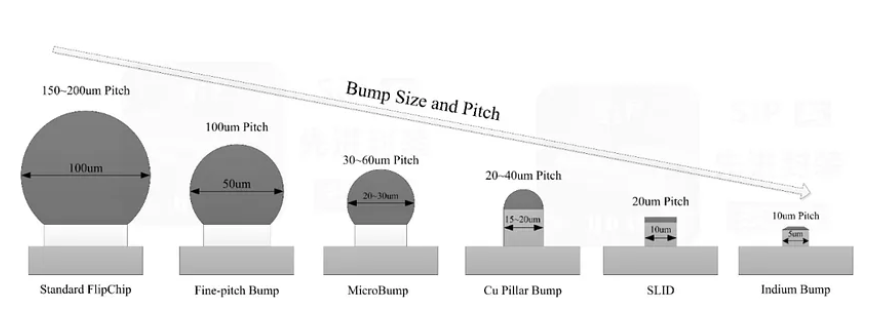

技術作用:Bump的尺寸和密度對芯片封裝的整體性能起著重要作用,尤其是在微型化封裝(如倒裝芯片技術Flip-Chip)中,凸點的大小和排列會直接影響封裝的可靠性和散熱性能。

現代無鉛材料如銅柱Bump替代了傳統的錫鉛合金凸點,不僅在環保方面更優,還具有更高的導電性和機械強度,適合高性能計算和移動設備。

為什么Bump是四大要素之一:Bump承擔著實現芯片與部基板的可靠電氣連接,并確保穩定的信號傳輸。它是實現芯片封裝接口的核心技術,直接影響芯片的散熱、導電性和機械強度。

3. RDL(Redistribution Layer,重布線層):重新分配電氣信號

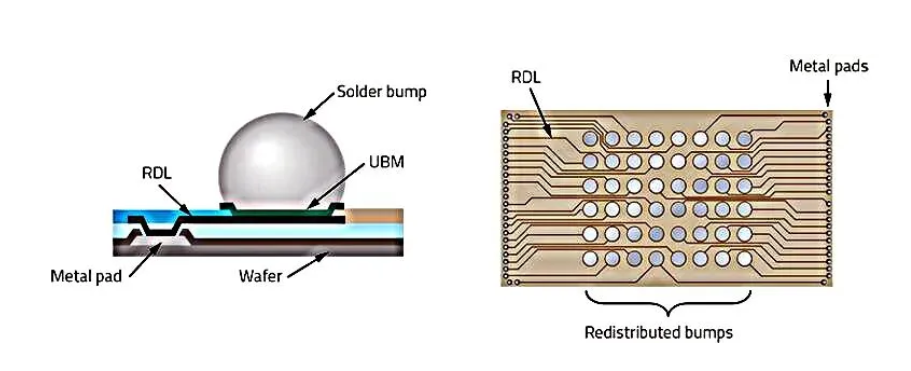

RDL是用于在芯片封裝中重新分配電信號的金屬層,類似于一座城市中的道路網絡。它通過改變芯片上引腳的布局,實現更高密度的信號連接,從而在有限空間內提高封裝性能。

技術作用:RDL能夠擴展和重新分配信號路徑,將芯片上的輸入/輸出引腳(I/O)從密集區域重新布線至較大區域,避免傳統封裝中引腳密度不足的問題。

現代封裝中,RDL層的設計已經從單層發展為多層結構,以應對復雜信號和高密度集成的需求。尤其是在Fan-Out(扇出型)封裝和WLP(晶圓級封裝)中,RDL的精細化布線技術成為核心。

為什么RDL是四大要素之一:RDL通過重新布線,有效提升了芯片的I/O密度和信號傳輸效率,能夠支持多層電路互連以及先進封裝中的異質集成。這使其成為封裝高性能化和小型化不可或缺的技術。

4. TSV(Through-Silicon Via,硅通孔):實現垂直方向的電氣互連

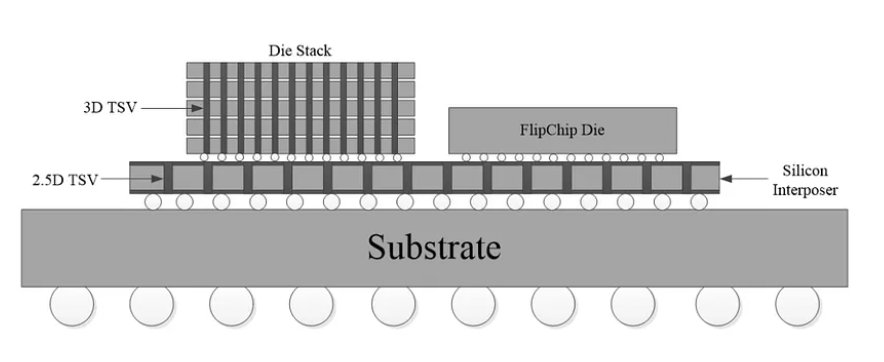

TSV 是一種在硅片中開孔,允許電信號在芯片的不同層之間垂直傳輸的技術,主要用于3D集成電路和2.5D封裝。

技術作用:通過TSV技術,芯片可以通過垂直方向的電氣互連,實現多層芯片堆疊,顯著提高了芯片的互連密度和集成度,降低了信號延遲和功耗。

2.5D TSV通過轉接板(interposer)將多個芯片集成在一起,而3D TSV則通過芯片直接垂直堆疊,實現更高的集成度和效率。

為什么TSV是四大要素之一:TSV為垂直方向上的芯片互連提供了有效解決方案,特別是在3D封裝中,TSV可以大大縮短信號傳輸距離,提升芯片集成度,適應了高性能計算和AI芯片對高效能的需求。

小結一下:Wafer、Bump、RDL和TSV是先進封裝中的四大關鍵技術要素,它們分別從材料基礎、連接、信號分配和垂直互連四個角度,解決了高性能封裝中的不同問題。Wafer是芯片封裝的載體,Bump連接芯片與外部基板,RDL優化了信號布線,TSV則實現了垂直互連。它們共同推動了半導體封裝技術向更小尺寸、更高密度和更高性能的方向發展。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號