服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2024-08-13作者來(lái)源:薩科微瀏覽:940

今天上午在深圳搞了一場(chǎng)封裝沙龍,探討先進(jìn)封裝的發(fā)展趨勢(shì),來(lái)了很多產(chǎn)業(yè)大佬。紀(jì)要如下:

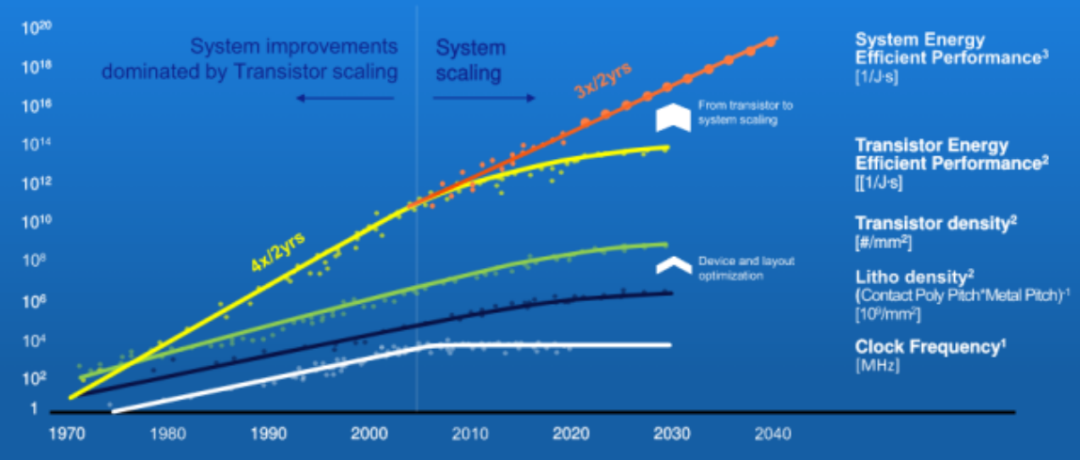

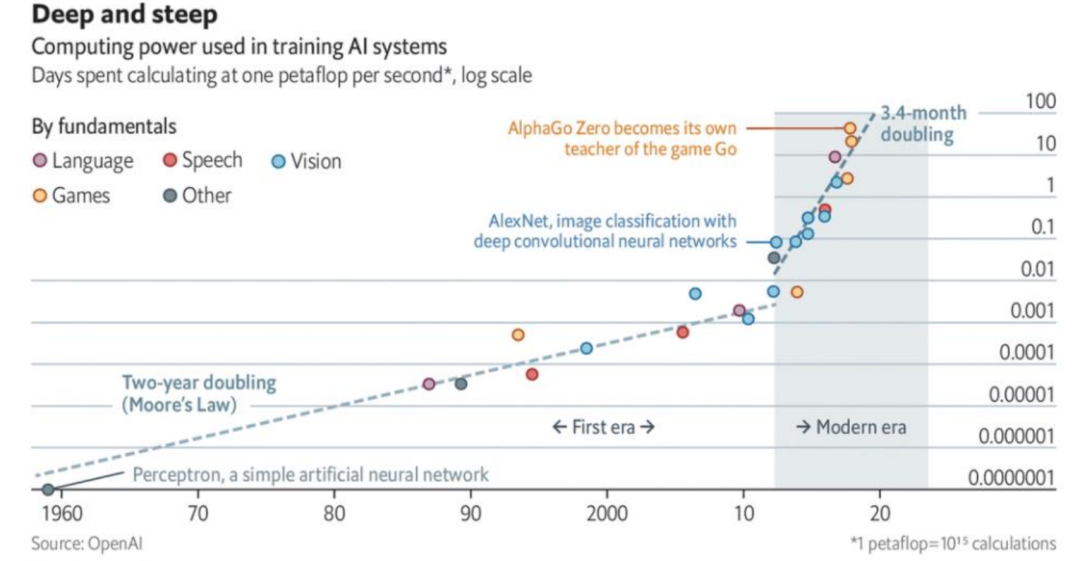

摩爾定律從1965年提出來(lái)后,發(fā)展了接近60年。不過(guò)自2005年后發(fā)展速度已經(jīng)放緩,但還在延續(xù),臺(tái)積電[敏感詞]的制程已經(jīng)來(lái)到2納米。

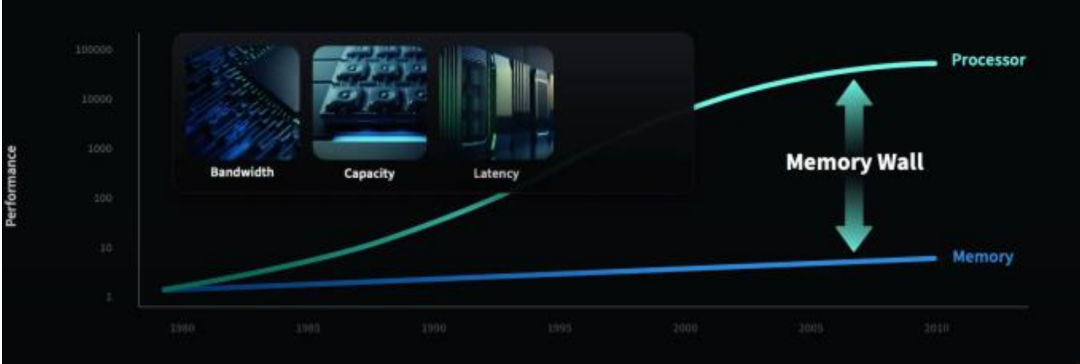

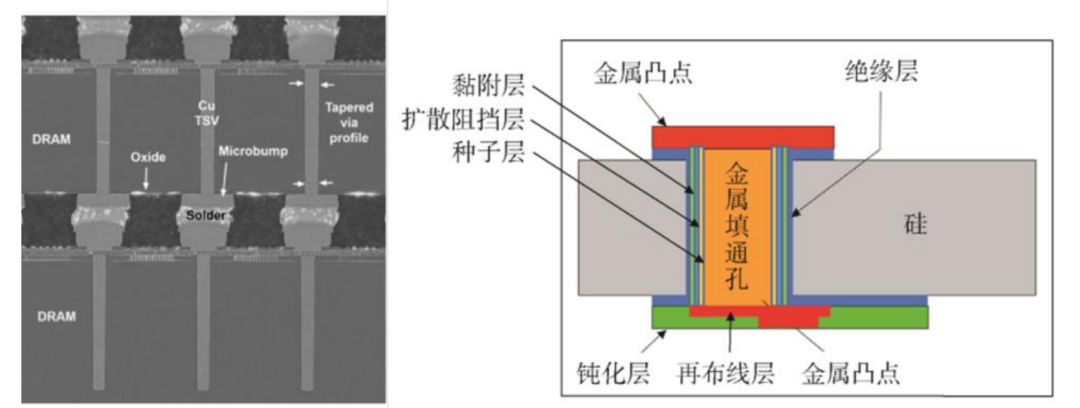

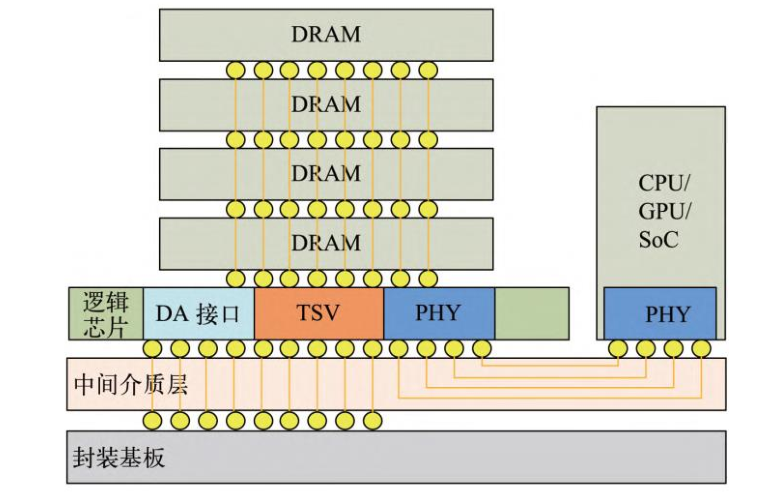

大芯片(CPU、GPU、AI芯片)存在三座大山:面積墻、功耗墻、存儲(chǔ)墻。存儲(chǔ)墻是因?yàn)樘幚砥魉俣忍欤鎯?chǔ)DRAM帶寬增長(zhǎng)太慢導(dǎo)致。HBM就是針對(duì)存儲(chǔ)強(qiáng)問(wèn)題誕生的,DRAM和DRAM之間通過(guò)混合鍵合的方式形成,目前做的[敏感詞]的是海力士,其次是三星、美光,國(guó)內(nèi)長(zhǎng)鑫存儲(chǔ)也在發(fā)力這塊。

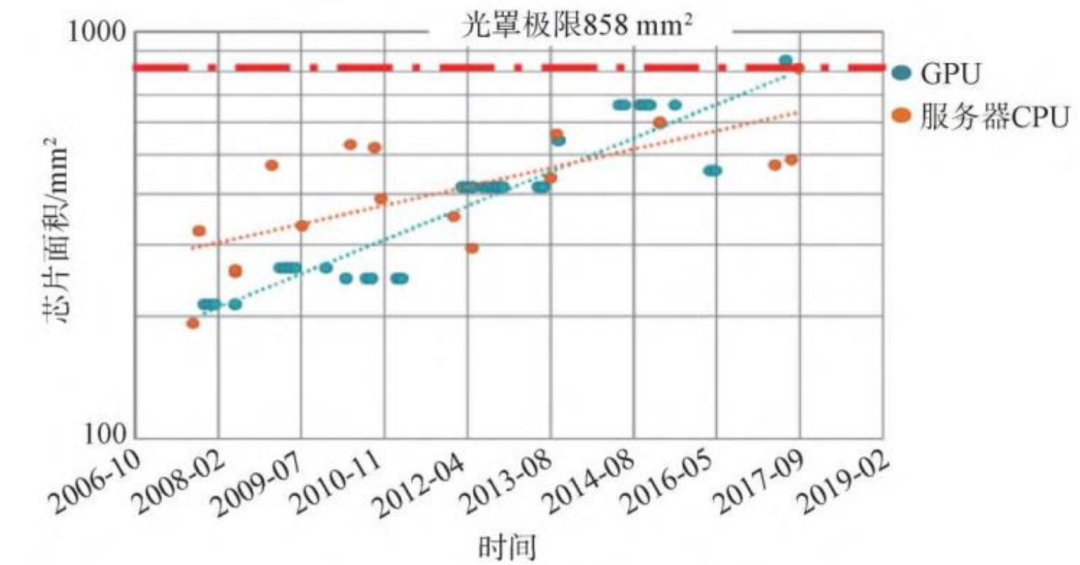

面積墻是AI對(duì)算力要求越來(lái)越高,GPU、CPU面積越做越大,但生產(chǎn)芯片的光罩面積存在上限導(dǎo)致。

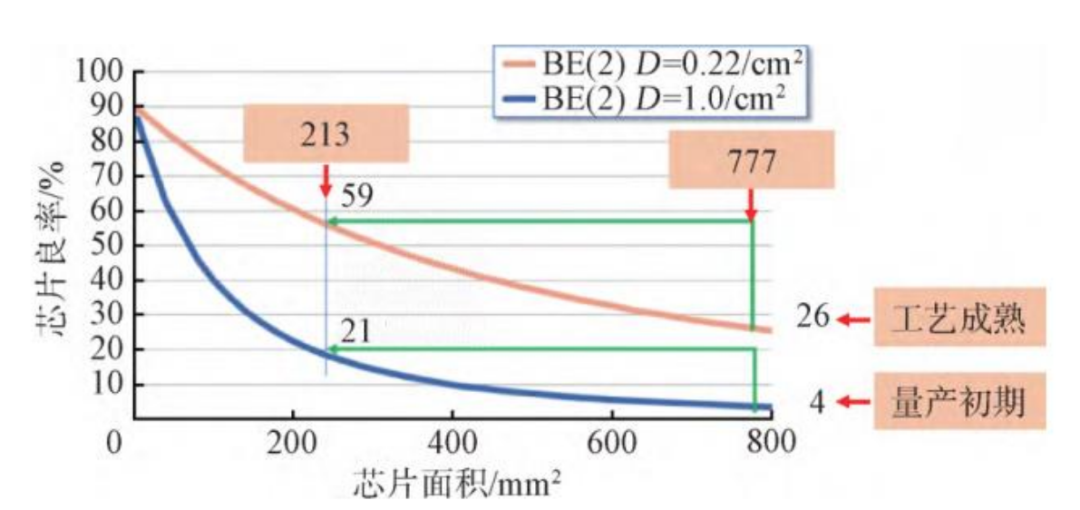

然而,芯片面積越大,制造的良率越低,芯片的成本越高。

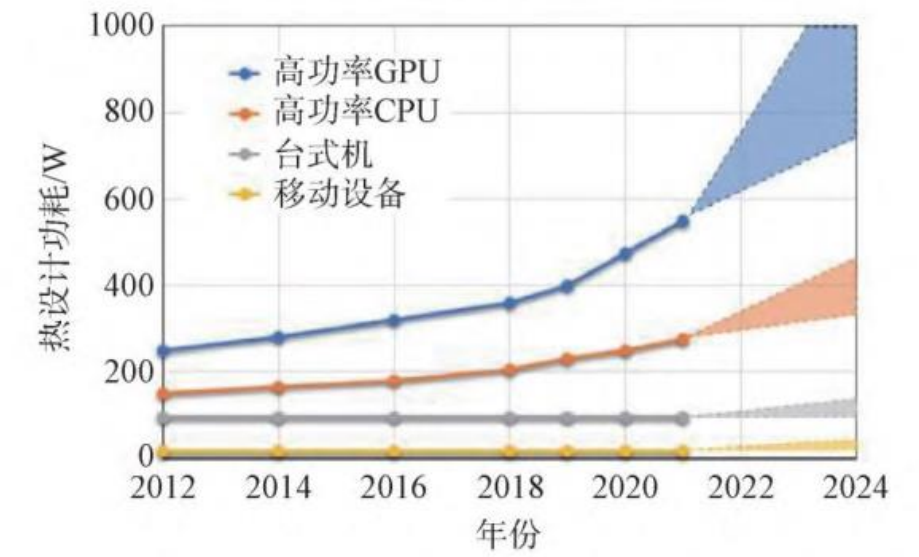

芯片算力越高,功耗越大,功耗墻問(wèn)題始終存在。

AI大模型對(duì)訓(xùn)練算力的需求:一是永無(wú)止境,多多益善,算力越大,大模型優(yōu)化越好;二是算力提升的速度遠(yuǎn)超摩爾定律的發(fā)展,所以GPU芯片需求很旺盛,僅靠傳統(tǒng)的制程微縮難以滿足AI算力需求。

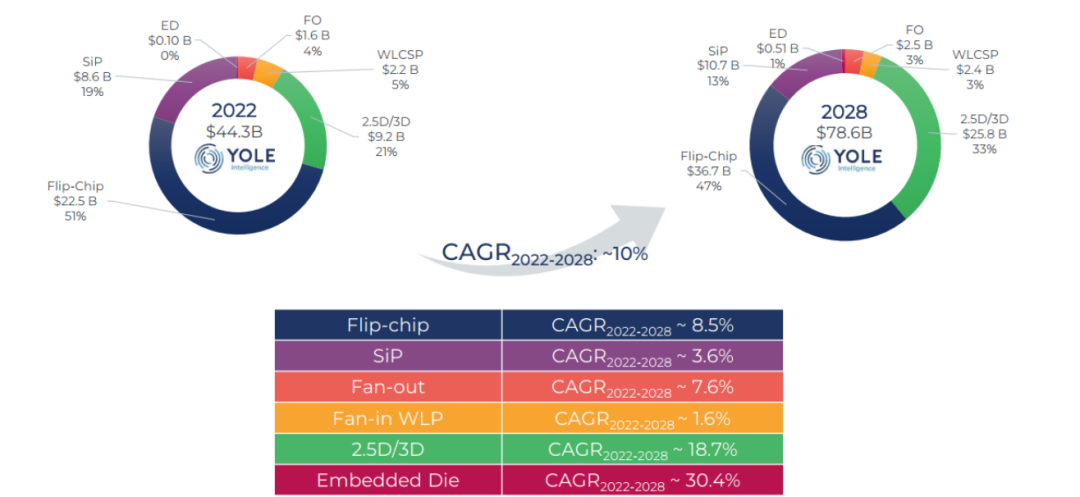

先進(jìn)封裝就是當(dāng)下提升算力、帶寬以及解決存儲(chǔ)墻、功耗墻和面積墻的重要方式之一。2.5D/3D等先進(jìn)封裝未來(lái)的需求很旺盛。

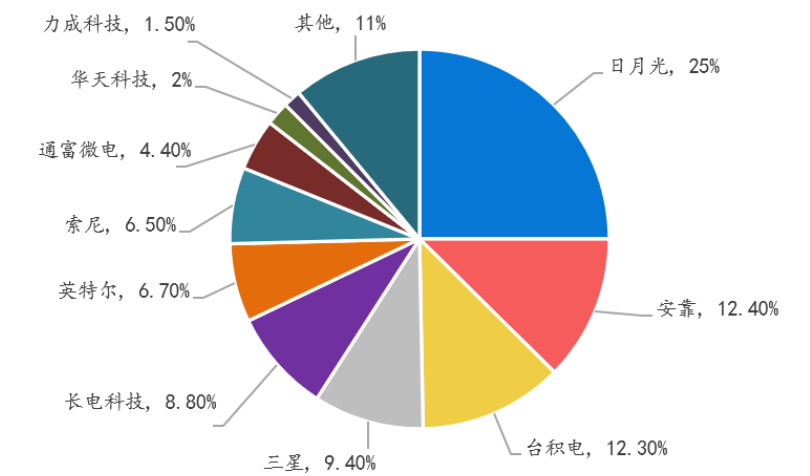

當(dāng)前,先進(jìn)封裝市場(chǎng)仍然被日月光、安靠、臺(tái)積電等主導(dǎo)。

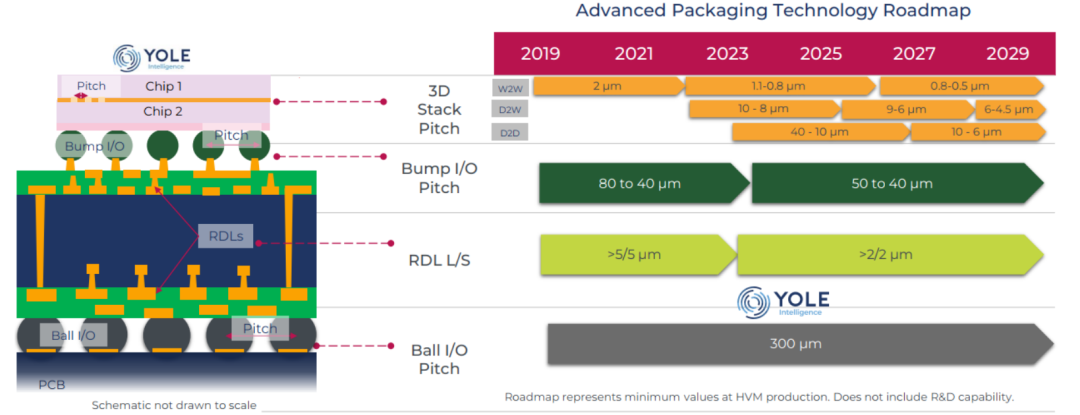

2.5D/3D先進(jìn)封裝未來(lái)的發(fā)展趨勢(shì):bump做小,bump之間的間距做小,布線的線寬線距做小,W2W、D2W、D2D的堆疊間距做小。

2.5D/3D先進(jìn)封裝的核心技術(shù)包括bump、TSV、RDL等。

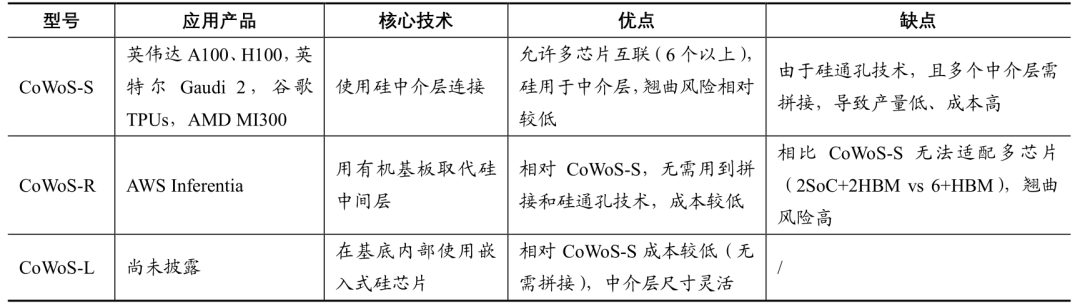

由于AI算力需求爆發(fā),臺(tái)積電的COWOS封裝當(dāng)前供不應(yīng)求,還在持續(xù)擴(kuò)產(chǎn)。

HBM技術(shù)解決了內(nèi)存的帶寬問(wèn)題,特點(diǎn)是高速、高帶寬,能夠滿足大模型訓(xùn)練要求,目前已經(jīng)演進(jìn)到第四代。HBM的核心技術(shù)包括TSV、BUMP、Wafer支撐系統(tǒng)、芯片堆疊/底部填充、鍵合等。

免責(zé)聲明:本文采摘自“老虎說(shuō)芯”,本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識(shí)產(chǎn)權(quán),轉(zhuǎn)載請(qǐng)注明原出處及作者,如有侵權(quán)請(qǐng)聯(lián)系我們刪除。

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專(zhuān)賣(mài) 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號(hào)-1