服務熱線

0755-83044319

發布時間:2024-09-06作者來源:薩科微瀏覽:1659

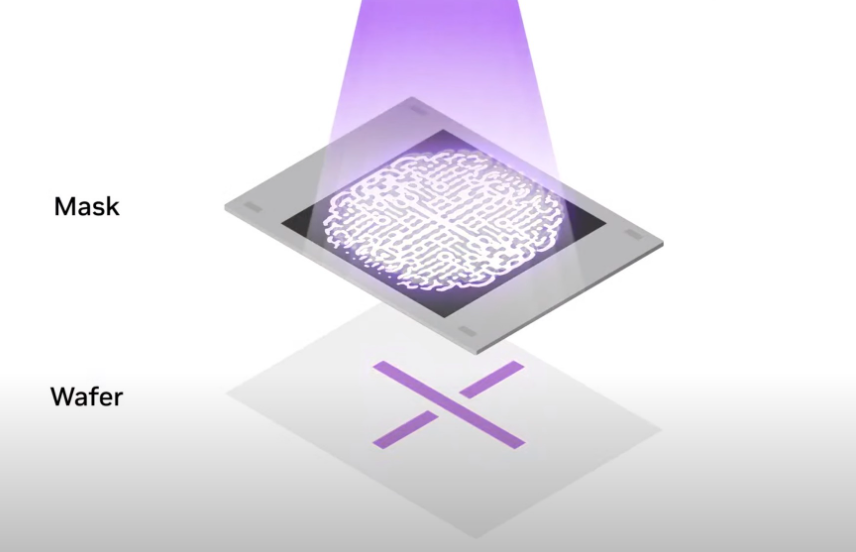

在集成電路工藝中,“full-mask”是一個關鍵概念,它涉及到半導體制造過程中掩模版的使用。掩模版是半導體光刻工藝中用于硅片表面圖案化的光學工具。掩模版上有微小的圖案,這些圖案將通過光刻過程轉移到硅片的光刻膠上,從而定義了芯片的功能區和布線層。

1、掩模版的基本作用

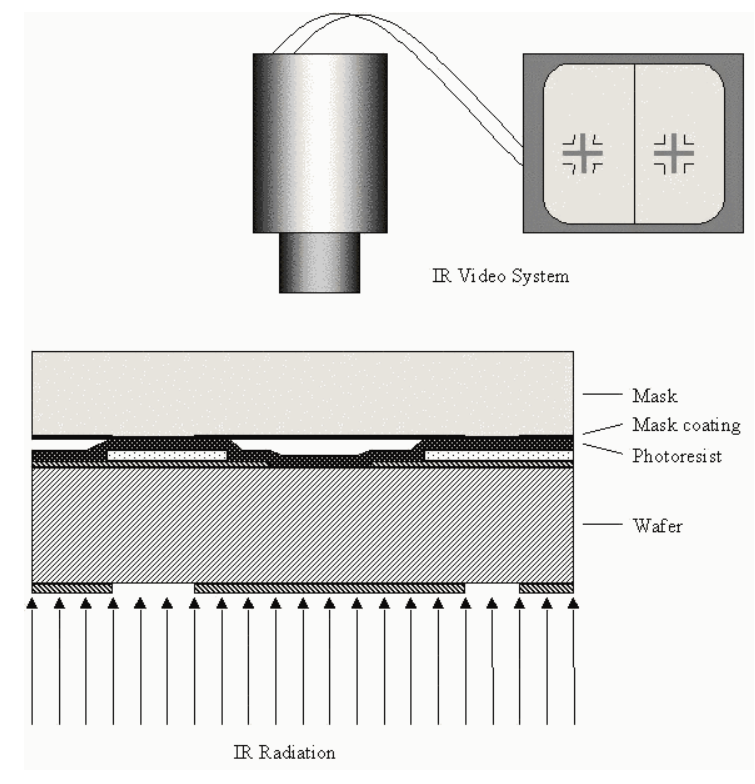

掩模版是用于在晶圓上創建特定圖案的工具。在半導體制造過程中,光刻是關鍵工藝步驟之一,通過曝光、顯影等步驟將掩模版上的圖案轉移到光刻膠上。掩模版的圖案通常代表了一個或多個器件層,如柵極、接觸孔、金屬互連等。

2、掩模版的分類

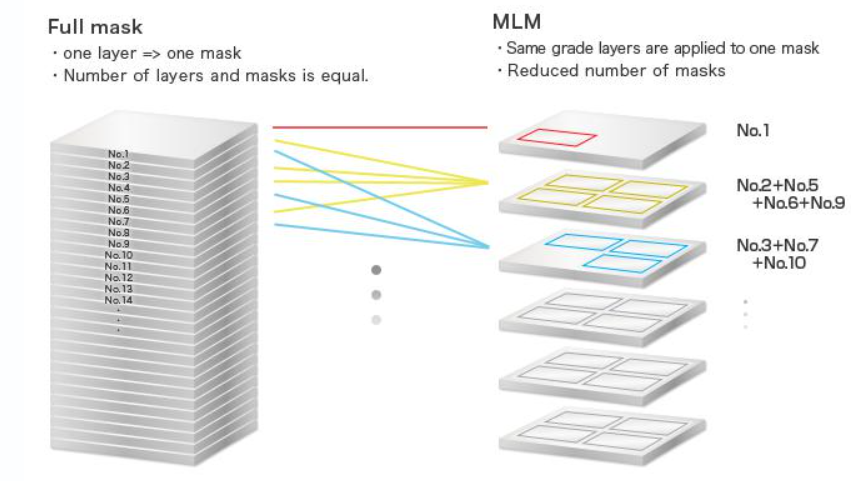

在集成電路制造中,掩模版可以分為兩種主要類型:

Full-mask(完整掩模版):覆蓋整個晶圓的掩模版,通常用于完整芯片的曝光。這種掩模版的圖案會精確地覆蓋晶圓的整個曝光區域,適用于大規模生產。

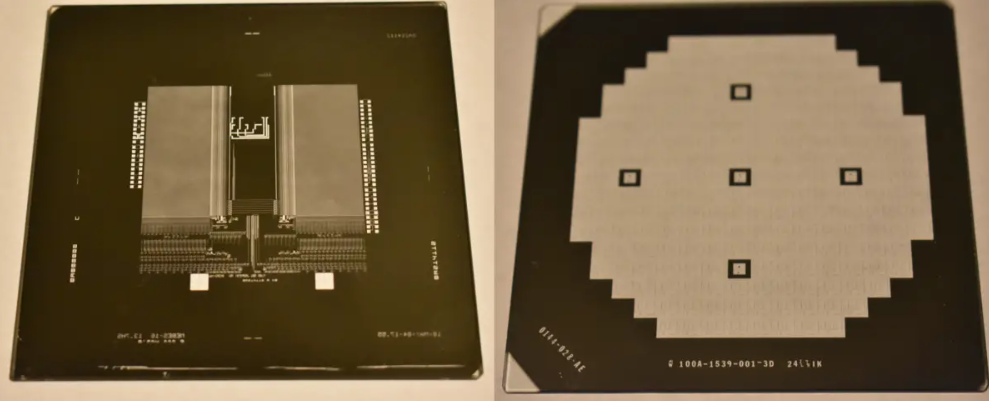

Reticle(部分掩模版):相較于full-mask,reticle通常覆蓋晶圓的一部分,每次曝光后需要移動光學曝光系統的步進掃描儀進行重復曝光,以覆蓋整個晶圓。

圖:reticle

3、Full-mask的詳細定義

Full-mask是指一種完整掩模版,在曝光過程中它一次性覆蓋并暴露整個晶圓或一個大面積區域的圖案。這種掩模版的優勢在于:

效率高:在生產中能夠一次性完成一個或多個芯片區域的圖案轉移,無需多次曝光,適合量產。

精度高:減少了重復曝光中的對準誤差,提高了圖案的精度和一致性。

成本高:因為其覆蓋范圍廣且圖案復雜,制作full-mask的成本較高,一旦設計發生更改,需要重新制作掩模版。

4、芯片設計流程

在芯片設計流程中,“full-mask” 通常是指在光刻(lithography)過程中使用完整的掩模版(mask set)。這種掩模版包含芯片制造的所有層級所需的掩模,是用于全芯片制造的完整套裝。芯片設計流程大致包括前端設計、后端設計以及制造三個主要階段:

前端設計(Front-End Design): 包括設計規格定義、RTL 設計、綜合、功能驗證等。這些步驟主要是對芯片的功能性進行設計。

后端設計(Back-End Design): 包括布局布線、時序分析、功耗優化、版圖設計等。這些步驟確保芯片的物理實現符合設計要求。

制造: 通過光刻、刻蝕、沉積等工藝步驟,將設計在硅片上實現。

5、掩模版(Mask Set)在芯片制造中的作用

在制造過程中,掩模版是光刻工藝中的關鍵部分。掩模版上包含了芯片設計的每一層的圖案,這些圖案通過光刻工藝被轉移到硅片上。每一層圖案都會定義芯片的某個結構,如柵極、源漏區、金屬互連等。

Full-Mask:Full-Mask 指的是一整套掩模版,涵蓋芯片制造中所需的所有層次。對于一個完整的芯片制造流程,可能需要幾十甚至上百張掩模版,每張掩模版對應一個工藝步驟(例如不同的金屬層、接觸孔、柵極結構等)。

作用:Full-Mask 用于全量產的生產,這意味著所有掩模都經過驗證,能夠用于大規模生產,以確保生產的芯片符合設計規格和質量要求。

6、Full-Mask在芯片生產中的關鍵步驟

設計驗證: 在生成掩模版之前,需要對設計進行全面的驗證,包括DRC(Design Rule Check),LVS(Layout vs Schematic),以及DFM(Design for Manufacturability)檢查。這些驗證步驟確保設計能夠被制造并達到高良率。

掩模制作: 基于驗證通過的設計文件,制作每一層的掩模版。掩模版的制作精度直接影響到最終芯片的特征尺寸和性能。

光刻過程: 使用掩模版將設計的圖案轉移到硅片上。這個過程涉及曝光、顯影、刻蝕等多個步驟,精度和對準誤差的控制是確保芯片性能和良率的關鍵。

生產驗證與優化: 使用 full-mask 進行首批試產,驗證工藝流程和產品性能,確保所有關鍵參數都在規格范圍內。如果發現問題,需要進行工藝優化和掩模修正(Mask Revision)。

量產導入: 一旦試產驗證通過,full-mask 進入量產階段,確保大批量生產的芯片一致性和性能達到預期。

7、Full-Mask 與 Reticle Limitations

在先進節點中,由于圖案尺寸的不斷縮小和復雜性增加,可能會遇到掩模視場(reticle field size)限制。為解決這一問題,通常會使用多重曝光(Multi-Patterning)技術,或對設計進行裁剪以適應掩模版的限制。

8、Full-mask的技術挑戰

在先進制程中,隨著節點尺寸的縮小(如28nm及以下節點),full-mask的制作變得更加復雜,因為圖案的分辨率和精度要求更高。這種情況下,full-mask的挑戰包括:

光學分辨率限制:掩模圖案需要適應光刻機的分辨率極限,因此通常需要使用OPC(光學鄰近校正)和其他掩模增強技術來提升圖案質量。

設計規則復雜性:隨著工藝節點的縮小,掩模設計需要考慮更多的電性效應和光學效應,如散射和衍射。

挑戰: 在更先進的制程中(如7nm及以下),掩模版的制作變得更加復雜和昂貴。每一層掩模的制作時間和成本都很高,需要確保設計的每個細節都完美無誤。

解決方案: 通過優化工藝流程、改進掩模版的制造技術(如EUV光刻),以及在設計階段進行全面的DFM優化,可以減少full-mask相關的挑戰,提升生產效率和良率。

隨著節點的縮小和設計復雜性的增加,full-mask的設計和制造面臨越來越大的技術挑戰,需要依賴先進的光刻技術和掩模增強方法來保證最終的圖案質量。full-mask是半導體制造中一個重要的光刻工具,尤其在大規模量產中具備效率高和精度好的優勢。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號